Realize special instructions on clustering VLIW DSP: multiplication-accumulation instruction

BWDSP is a 32bit static scalar digital signal processor with VLIW and SIMD features, which is designed for high-performance computing. Associated special instructions are designed for its special architecture and application scenarios. However, the e…

Authors: Binbin Liu, Qilong Zheng

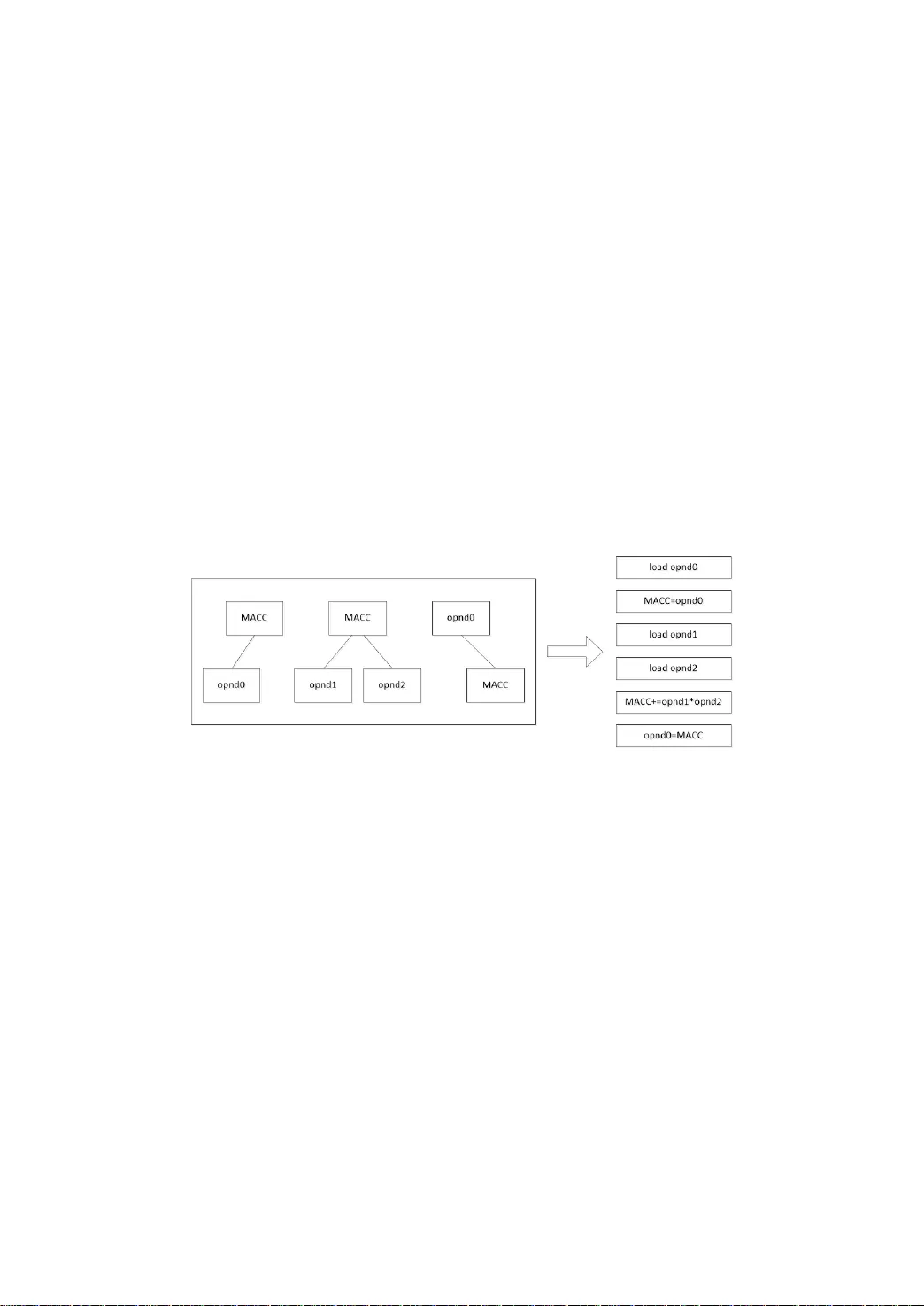

分簇 VLI W DS P 上 特 殊 指 令实 现 之 乘法 累 加 指 令 刘 彬 彬 1, 2 , 郑 启 龙 1 , 2 1 ( 中 国科 学 技 术 大 学 计 算 机科 学 与 技 术 学院 , 安徽 合肥 23 002 7 ) 2 ( 安 徽省 高 性 能 计 算重 点 实 验 室 , 安徽 合肥 2 30 027 ) 通讯作者 : 刘 彬 彬 , E -ma il : rob be rt l@ mai l.u st c. edu .c n 摘 要 : BWDSP 是一款采用 VLIW 和 SIMD 架构 , 针对高性能计算领域而设计的 32 位静态标量数字信号处理器 . 针对其特殊的体系结构和特定的应用场 景 , 设计了一系列相应的特殊指令 . 然而现有的编译框架 , 并没有对这些特殊 指令提供支持 . 因此 , 在传统的 Open64 编译器的框架下 , 针对 BW DSP 结构特点 , 提出了一种实现特殊指令的算法 , 通 过该 算法实 现 了乘法 累加 指令 , 以提 高具有 乘法 累加 需求 算法的 性能 . 实验 结果 表明 , 针 对相 关算 法 , 该实 现能 够在 BWDSP 上取得最高 8.85 倍的加速比 . 关键词 : 编译优化 ; 分簇体系 DSP; 单指令多数据流 ; 特殊指令 ; 乘法累加指令 中 图 法 分 类 号 : TP 3 11 Re aliz e s pec ia l i ns tru ct ion s on clu s ter ing VLI W DS P : mult ip lica tio n -a ccu mul at ion inst ruc ti on Bin b in Li u 1, 2 , Qi l ong Zh en g 1, 2 1 (Sc ho ol of Com pu te r Sci en ce and Te ch nolo gy, Uni ve rsi t y of Sc ie nce a nd Tec hn olog y of Ch in a, He fei 2 30 027 c hi na) 2 (Ke y Labo rat or y o f Hi gh Pe rfor ma nce C omp uti n g An hu i Pro vin ce , He fei 23 00 27 ch in a) Abs tr act : B WDSP is a 32bi t st ati c sc alar di git al sign al p roce ss or wit h VLIW an d SIM D feat u res , wh ic h is d esi gn ed for hi gh -pe rfor man ce com pu ti n g. A sso ciat ed sp ec ia l in st ru cti ons ar e de si gn ed fo r i ts sp eci al arc hi te ctu re and ap pli ca tio n s cen ar ios . Howe ver, th e exis ti ng co mpi lat ion fram ewor k doe sn ’t mee t thes e spe ci al inst ru ct ions . Th ere fore , in th e con tex t of trad i tion al Ope n64 comp ile r, pr opo sed a sp eci al instr uct io n alg ori th m. Thr ough thi s alg ori th m imp le men ts th e mu lti p lic ati on -ac cu mu lat io n ope rat i on wit h BW DSP st ru ctu re , to imp ro ve t he p er forma nc e o f a lgor it h ms w ith mu lti pl y -a ccu mu lat e re qui re ment s . Ex pe rmen ta l r esu lts sh ow t ha t th e a lgor it hm , whi ch c an ma ke an ma xi mum of 8 .8 5 s pe edu p o n BWDS P . Key w or ds : c omp il er opt i miz ati on ; mul ti -clu s ter DS P; S IMD; s pe ci al in st ruc ti ons ; mu lt ip lic ati on -ac cu mu lat ion op era ti on DSP 广泛 应 用 在 调 制 解 调 器 、 数 字图 片、 多 媒 体计 算 等 系 统 中 . DSP 的应 用 和 通 用 处 理 器 有 很 大 的 不 同 , 经 常 被 应 用 在 迭 代 和 计 算 强 度 很 大 的 数 字 信 号 处 理 中 . DS P 最 早 引 入 实 现 快 速 乘 法 累 加 计 算 的 硬 件 乘 法 器 , 该 乘 法 器 通 常 对 应 一 条 加 速 信 号 滤 波 的 特 殊 指 令 — M ACC 指 令 这 条 指 令 是 根 据 滤 波 算 法 一 个 重 要 公 式 (1 - 1) 而 设计 , 应用 M AC C 指 令 能 大 大 加 速 滤 波 算 法 的 运 算速 度 . n i i n i x n x 0 ) ( ) ( ) ( (1 - 1) 为了 提 高 特定 应用 环 境 下的 运 行 速 度 ,D SP 增加 了 许 多 特 殊 的 指 令 和 功 能 单 元 , 这使得 DS P 的 结 构 和通 用 处 理 器的 结构 有 了 很大 的 不 同 , 也对 我们 实 现 这些 特殊 指 令 提出 了很 大 的 挑战 . 本文 对 特 殊指 令 — M AC C 指 令 的 实 现 进 行 讲 解 . 根 据 目 标 DS P 的多簇架构 和 SI MD 编译 优 化 , 结 合 特 殊 指 令的 具 体 要求 , 在 编 译 器 后 端 , 添加 相关 特 殊 指令 , 修 改 相 应 处 理 流 程 , 以实 现 M A CC 指令 . 本文 第 1 节 介 绍 目 标 DS P — B WDS P 和 相 应 编 译 器 — O p en6 4 编 译 器 的 基本 框 架 . 第 2 节 提出 了 一 种 实 现 DSP 上 特 殊 指 令 的 算法 框 架 . 第 3 节根据第 2 节 的 算 法 , 结合 O pen 64 编 译 器 和 BWD SP , 介绍 M ACC 指令 的实 现 过程 . 第 4 节对 M AC C 特殊 指 令 的 实 现 进 行 测 试 和 结 果 分 析 . 最 后 总 结 全文 , 并 提 出 未 来 可 以 进 一 步 提高 优化 的 方面 . 基金项目 : 核高基重大专项 (2 0 12 ZX01 034 - 001 -0 01 ) ; 2 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 1 研究背景 BWD SP 是 一款 针 对 高 性 能 计 算 领 域 而 设 计的 32 位 静 态 标 量 D SP , 采用 V LI W( 超 长指 令 字 ) 、 SI M D( 单指 令多 数 据 流 ) 架构 , 其 内 核 由 4 个构 造 完 全 一 致 的 基 本 执 行 簇 组 成 , 分 别 为簇 x, 簇 y , 簇 z, 簇 t , 结 构 如 图 1 所示 [2 ]. 每个 簇 有 8 个 算 术 逻 辑 运 算 单 元 ( AL U), 8 个 乘 法 器 (M U L), 4 个 移 位 器 ( S HF ),1 个 特 殊功 能 单 元 (S PU ). 此外 , 该处 理器 内 部 还有 三个 结 构 相同 的 地 址 产生 器 u 、 v 、 w , 用 来 执 行 地 址 运 算 指 令 和 访 存 指 令 . 簇 X 簇 Y 簇 Z 簇 T Fi g. 1 B WDS P s tru ct ur e 图 1 B WD SP 主 要 结 构 BWD SP 编译器 , 是 基 于 开 源 编 译 器 Op en 64 [ 3] 作 为编 译 器 研 究 框 架 , 其 主 要 工作 在 于 后端 重定 向 和 针对 特 定 体 系 结 构 的 优 化 .Op en 64 完 善 的 前 端 处 理 功 能 能 够 将 源 程 序 代 码 转 化 成 相 应 的 层 次 化 的 中 间 表 示 — WHI R L, 支 持 全 程 序 的 分 析 优 化 , 功 能 强 大 . 同 时 又 具 有 很 好 的 移 植 性 , 后 端 支 持 多 种 体 系 结 构 , 包括 M IP S 、 Ita ni u m 、 AR M 、 AMD6 4 、 X 8 6 - 64 、 I A32 、 NV IDI A 等 . Op en6 4 的前端 将 源 程 序 转 化 为 中 间 表 示 WHI R L[ 4] , 后 端 读 入 WH IR L, 翻 译 成 代 码 生 成 阶 段 (C od e Gen er ati on , CG ) 的 中 间 表 示 C G IR , 在 经 过 一 系 列 优 化 , 最终 CG IR 经 过 代 码 输 出 生 成 汇 编 程 序 [ 3] .O pen 6 4 编译器 的架 构 如 图 2 所示 . 主要驱动程序 后端驱动 (*)IPL+(*)IPA-LINK AS+ 链接器 前端驱动 C/C++ (*)IPA PreOpt/LNO/Wopt/CG .o exec (*).I .B (*)= 可选项,如 -IPA 被打开 .s Fi g. 2 O pen 6 4 co mpi la tio n mo de l 图 2 O pe n6 4 编译 架 构 在 B WDS P 的 指 令 集 中 , 拥有 32 位定 点 乘 法 累 加 指 令 , 双 16 位 定 点 乘 法 累 加 指 令 , 16 位定 点 复 数 乘 法 累 加 指令 , 32 位 定点 复 数 乘 法 累加 指 令 [ 1 ] . 针 对 乘法 累加 指 令 (M AC C 指令 ), BW DS P 每 个 簇 拥 有 4 个 专 用 乘 法 累 加 寄存 器 (M AC C0 /1 /2 /3 ), 用以 加 快 乘 法累 加运 算 的 速度 . 在 B W DSP 指令 执 行 过 程 中 ,1 个乘 法 指令 需 要 3 个时 钟 周期 ,1 个 加 法 指 令 需要 1 个 时 钟 周 期 ,1 个 乘 法 累 加指 令仅 需 要 1 个时 钟 周 期 , 故 乘法 累加 指 令 的 执 行 效率 是 非 常高 的 . 2 特殊指令实现的算法框架 针 对 该 体 系 结 构 的 特 性和 特 定 的 应 用 场 景 , 设计了一系列特殊的指令 , 包 括 位 反 序 寻 址 、 乘 法 累 加 / 累 加指 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 3 令和 移 位 器查 找表 指 令 等 . 结合 B WDS P 的 特 殊 指令 和 Op en 6 4 编 译器 架 构 , 本 文 提 出 特 殊 指 令 的 实 现算 法 , 包括 以下 4 个 步 骤 : (1 ) 建立 特 殊 指 令 的 实 现 模 型 . 根 据 特 殊 指 令 的 具 体 情 况 , 结合 Op en 64 编 译 器 后 端 中 间 语 言 表 示 和 处 理 流程 , 建立 合 适 的 特 殊 指 令 实 现 模 型 . (2 ) 特殊 指 令 的 资 源 约 束 分 析 . 特 殊 指 令 一 般 由 专 门 的 硬 件 驱 动 , 由 于 资 源 的 限 制 , 特 殊 指 令 的 实 现 也 需 要满 足 一 定的 约束 条 件 . (3 ) 在机 器 描 述 中 加 入 特 殊 指 令 [ 11]. Op en6 4 编 译 器 的 机 器 描 述 采 用 二 次 编 译 形 式 , 简 化 了 对 指 令 、 c pu 建模的操作 . 对 于 特 殊 指 令 的 实 现 , 首 先 需 要 在 机 器 描 述 文 件 中 增 加 相 应 的 指 令 描 述 , 供 编 译 器 在 运 行时 使 用 . (4 ) 特殊 指 令 的 实 现 . 在 O pe n6 4 编译 器 后端 编译 优 化 处 理 流 程 中 , 根 据 特 殊 指 令 的 实 现 模 型 和 相 关 的 资 源约 束 分 析 , 实 现 特 殊 指 令 及 其 相 应的 处 理 流程 3 乘法累加指令的实现 由于 B WD SP 的 特 殊 结 构 和 乘 法 累 加 指 令 的 特 殊 性 , 在 对 乘 法 累 加 指 令 实 现 的 过 程 中 , 对 编 译 器 后 端 相 关 模 块 都 有 影 响 , 因 此 需 要 进 行 相 应 的 修 改 . 相 关 模 块 包 括 机 器 描 述 、 指 令 注 释 、 寄 存 器 分 配 和 汇 编 指 令 生 成 等 阶段 . 本文 选 择在 Op en6 4 编 译 器的 中间 语 言 WH IR L 上 , 进 行 乘 法 累加 指令 的 合 成 , 参 考 本 文 提 出 的 特 殊 指 令 实 现算 法 , 相 应 步 骤 如 下 . 3. 1 建立 乘 法 累加 指令 的 实 现模 型 在编 译 器 前端 , 1 条 乘 法 累 加 指 令 , 被 拆分 成 1 条 乘 法 指令 和 1 条加 法 指 令 . 故 乘 法 累 加指 令 的 查 找 模 型为 op nd 0= ADD (o pn d 0, M UL( op nd 1, o pn d2 )) , 替换 的 结果为 M AC C= opnd0 , M AC C += opnd1 *op nd 2 ,o pn d0 =MAC C. 替换条件为 : 1. 加法操作 ; 2. 一个操作数和一个乘法操作 ; 3. 输入的操作数是为了进行乘法操作 ; 4. 加 法 结 果 写 回 第一 个 操 作数 . 识别 和 替 换模 型如 图 3 所示 . Fi g. 3 M AC C i ns tr uc tio n r e cog ni ti on an d re pl ace me nt a lgo ri th ms 图 3 乘 法 累 加 指 令 识 别 和 替 换 模 型 3. 2 乘法 累 加 指令 的资 源 约 束分 析 乘法 累 加 指令 是 S IM D 向 量 化 [ 5] 的一部分 , SIM D 向 量化 位 于 编译 器后 端 的 循环 嵌套 优 化 中 . 由于 B W DSP 的每 个 簇 上 , 只有 4 个 乘 法 累 加 寄 存 器 , 故在 对源 程 序 的最 内层 循 环 进行 S IM D 向 量化 时 , 其乘 法 累 加 指 令 是 不 允许同时超过 4 条 . 如 果 超 过 了 硬 件 资 源 的 限 制 , 则 放 弃 合 成 . 在 满 足 硬 件 资 源 限 制 的 条 件 下 , 选 择 优 化 性 能 更 高、 收 益 更大 的 双字 指令 模 式 进 行 S I MD 向 量 化 [ 6] . 3. 3 机器 描 述 文件 Op en6 4 编 译器 框 架 采 用 了 二 次 编 译 的 方 式设 计 机 器 描 述 文 件 的 架 构 , 对 乘 法 累 加 指 令 的 支 持 通 过 填 写 相 4 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 应的 机 器 描述 [ 11] 模型文件 , 完成 B WDS P 相 应 的 寄 存 器 模 型 后 , 在 文 件 b w10 4x -o pc od es. kn b 和 o p cod e_ gen .c xx 中添 加 需 要支 持的 相 关 乘 法 累 加 指 令 描 述 , 然 后 编 译 机 器 描 述 文 件 , 生 成动 态 链 接库 供编 译 器 在运 行时 使 用 . 修 改 汇 编 代 码 输 出 格 式 . 对 相 关 乘 法 累 加 指 令 按 照 B WDS P 的 指 令 格 式 进 行 汇 编 代 码 输 出 , 汇 编 输 出 标 志 着编 译 器 代码 优化 以 及 完成 , 是在 c ge mit 阶 段 完成 . 在 文 件 i sa _p ri nt. c xx 和 tar g_i n fo/ is a/b w /i sa_ pa ck .c xx 文 件 中 , 增加 相 关 指令 的打 印 格 式 . 3. 4 乘法 累 加 指令 的实 现 3. 4. 1 乘 法 累 加 指 令 的 合 成 编译 器 后 端 , 将 前 端 生 成 的 gs pi n t re e 翻译为 h igh l ev el wh ir l 树 . 在 whi r l 树的 LNO ( 嵌套 循环 优 化 ) 处 理 阶 段 , 自顶 向 下 遍 历 最内 层 循 环子 树 , 根据 乘法 累 加 指令 的识 别 模 型 , 寻 找 满 足 条 件 的 子 树 . 寻找 到 相 关子 树之 后 , 进 行 相 应 的 替 换 . 在 最 内层 循环 前 , 将 M AC C 寄存 器 赋 初 值 为 opnd0 . 在 循环 中 , 合成 MAC C 指令 . 在 循 环 后 , 将 M AC C 寄 存 器 的 值 赋 值 给 opnd0 . 3. 4. 2 指 令 注 释 中间 语 言 W HI RL 经 过 逐 层 下 降之 后 , 代 码 生 成 阶 段 调 用 指 令 注 释 将 WH IR L 树 扩 展 成 与 机 器 指 令 一 一 对 应的 后 端 中间 表示 C GIR 指 令 序 列 . 由 于 指令 注释 依 赖 于目 标处 理 器 的机 器指 令 , 因 此需 要对 S IM D 指 令注 释 进 行特 殊 处 理 . 具 体 的 指 令 注 释 算 法 请 参 考文 献 [ 6] . 指令 注 释 示意 图如 图 4 所示 . Fi g. 4 i ll ust ra ti io n of M ACC in s tru ct io n co mme nt s 图 4 乘 法 累 加 指 令 注 释 示 意 图 3. 4. 3 指 令 分 簇 指令 分 簇 是指 把每 条 C GIR 指 令 指 定到 x 、 y 、 z 和 t 相应 簇 上 , 通 过 多 个 簇 同 时 执 行 来 实 现 并 行 . 具 体的 指 令分 簇 算 法请 参考 文 献 [7 ] . 3. 4. 4 寄 存 器 分 配 寄 存 器 分 配 是 为 每 个 虚 拟 寄 存 器 分 配 其 运 算 簇 上 面 的 实 际 寄 存 器 , 包括全局寄存器分配和局部寄存器分 配 . 由 于 乘 法 累 加 指 令 在 进 行 寄 存 器 分 配 时 , 已 经 跨 越 基 本 块 了 , 故 在 全 局 寄 存 器 分 配 阶 段 对 其 进 行 寄 存 器 的 分配 . Op en 64 全局 寄 存 器分 配采 用 图 着色 算法 , 同时 加入 了 优 先级 考 虑 以及 分裂 活 跃 区 间 的 概念 [ 9] . 在进行全 局寄存器分配的时候 , 优先考虑乘法累加等操作指令的处理 , 将 M ACC 指 令 分 配 到 专 用 的 乘 法 累 加 寄 存 器 中 , 然 后 再 考 虑 其 它 指 令 的 全 局 寄 存 器 分 配 . 局 部 寄 存 器 分 配 采 用 更 精 确 的 线 性 分 配 方 法 , 为 基 本 块 一 级 的 局 部 变 量分 配 寄 存器 [ 10 ] .S IM D 指 令 寄 存 器 分 配 主 要 在 局部 寄 存 器 分 配 阶段 , 具 体 分 配 算法 请参 考 文 献 [ 6] . 3. 4. 5 汇 编 指 令 生 成 对相 应 的 乘法 累加 指 令 , 按照 B WDS P 的 指 令 格 式 , 进 行 汇 编 代 码 输 出 . 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 5 4 实验结果和分析 本 文 针 对 BW DSP 的 特 定 架 构 和 特 殊 指 令 , 实 现 了 相 关 的 乘 法 累 加 特 殊 指 令 . 我 们 选 取 卷 积 运 算 、 向 量 点 积、 fi r 滤 波 算 法和 矩 阵 相乘 , 来 验 证 方 案 的 有 效 性 . 在 B W DSP 编 译 器 的 开 发 平 台 环 境 R ed H at En te rp ris e Li nu x 5 中 对 测 试 程 序 是 否 实现 乘 法 累加 指令 进 行 测 试 , 采 用 的 性 能 指 标 为 时 钟 周 期数 . 运用 B WDS P 的 调 试 器 E CS 来 测 量 优 化 前 后 生 成 的 汇 编 指 令代 码 的 时钟 周 期数 . 相关 结果 如 表 1 所示 . T abl e 1 Pe rfo rm anc e o f M AC C in st ruc ti on 表 1 M ACC 指令性能 测试 算 法 实现 前 周 期 数 实现 后 周 期数 加速 比 向量 点 积 ( N= 102 4 ) 17430 1969 8.8 5 卷积 运 算 ( N= 102 4 ) 19508 3289 5.9 3 fir 滤波 ( n =1 024 ,N =1 28) 209 9277 428 42 3 4.9 0 矩阵 相 乘 ( 1 00* 10 0) 231 01 21 5 41765 34 5.5 3 从上 表 可 以看 出 , 相关 算 法 的 加速 比 达 到了 5. 5~ 8 .8 倍 . 下面 以 向 量 点 积 为例 , 进 行 更 加 详 细 的 说明 . 测试 用 例 中的 向量 点 积 程序 如 下 : in t su m=0 for (i = 0 ;i < N; i+ +) { / /N= 10 24 su m + = a[ i] * b[ i ]; } 未实 现 乘 法累 加指 令 前 生成 的 汇 编 代码 : _Lt _0 _3 5 86 : xr11=[ u 5 +=1 ,0 ] // u5 为数组 a 的地 址 ||x r1 3= 1 ||x r1 4= 10 23 xr1 0= [u 6 +=1 ,0 ] // u 6 为数组 b 的 地 址 ||x r1 5= r1 5+ r1 3 xr11=r 11 *r10 .co de _a li gn 4 If xr1 5 != r1 4 B _ Lt_ 0_ 35 86 || xr1 4 =r1 4+ r1 1 _Lt _0 _2 0 50 : u6 =_ _su m // u6 为 su m 的值 [u 6 +0, 0] =xr 14 实现 乘 法 累加 指令 后 生 成的 汇 编 代 码 : _Lt _0 _2 5 62 : xyz tr1 3 =0 xyz tM AC C0= r1 3 xyz tM AC C1= r1 3 _Lt _0 _7 7 0: xyz t r1 9 :1 8 =[ u5 += 8, 1] // u5 为数组 a 的 地 址 ||x r1 7= 8 ||x r1 6= 10 23 6 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 xyz tr 21 :2 0= [u 6 += 8, 1] / / u6 为数组 b 的地 址 ||x r1 5= r1 5+ r1 7 xyz tM AC C0+ =r 19 *r2 1 .co de _a li gn 4 If xr1 6 >=r 15 B _ Lt _0 _7 70 || xyz tM AC C1 += r1 8 *r20 _Lt _0 _1 5 38 : u6 =_ _su m ||x yz tr 8=M A CC0 xyz tr9 = MAC C1 xyz tr8 = r8 +r9 xr1 0= si gma xyz tr 8 [u 6 +0, 0] =xr 10 从上面的汇编代码中可以看出 , 对于卷积运算 , 未实现乘法累加指令循环中的指令周期为 1 7 *10 24 =17 4 08 , 表中 周 期 略高 , 因 为 包 括 其 他 一 些 指 令 周期 在 内 . 实现 乘 法 累 加 指 令 后 指 令 周 期 为 1 5 *10 2 4/ 8= 19 20 , 包括循环前 的 乘 法 累 加 寄 存 器 赋 初 值 和 循 环 后 乘 法 累 加 寄 存 器 结 果 归 约 等 指 令 周 期 , 共为 1969 . 通 过 计 算 , 其 加 速 比 为 8. 85 . 5 结语 本文 针 对 B WDS P 分 簇 体 系 结 构 及 其 特 殊 指 令 , 在 Op en 64 编 译 器 基 础 设施 上 , 提 出 了 一 种 特 殊 指 令 实 现 算 法 , 并 按 照 该 算 法 , 成 功 实 现 了 其 乘 法 累 加 特 殊 指 令 , 并 且在 B WDSP 编 译 器 上 对实 现 效 果进 行 了 测试 和分 析 . 实 验结 果 表 明 , 可 取 得 最高 8 .8 5 倍 的 加 速 比 . 今后 , 需 要继 续 扩 展软 流水 方 法 、 零 开 销 循环 等 优 化 技 术 , 提 升 乘 法 累 加优 化 应 用性 能 . Ref ere nc es : [1 ] CETC 38 . B WDSP 10 0 s oftw are us er man ua l[R ]. H efei : Ch in a El ect ron i cs Te ch nol ogy G ro up Corp or ati on No.3 8 Re se arc h In sti t ute , 20 11 : 18 1- 19 7 . [2 ] CETC 38 . B WDSP 10 0 h ard war e u se r m an ua l[R ]. He fei : Ch in a Ele ct ron ic s Te ch nolo gy G rou p C orp ora ti on N o.3 8 Re sea rc h In sti tu te , 20 11 :1- 2. [3 ] Su i YL. Ope n6 4 Int ro du cti on [EB/ OL]. [ 20 1 6-9 -17 ]. h tt p:/ / www.c se .un s w.ed u.a u/ ~ys ui /sa be r/ open 64 .pd f . [4 ] Ope n6 4. Op en6 4 Com pi ler W hi rl Int er med ia te Re pre sen t ati on [ EB/ OL].[ 20 1 6-9 -1 7] . ht tp :// www. mc s. an l.gov /Op en AD/ op en6 4 A.pd f . [5 ] SIMD [E B/O L]. [2 01 6 -9- 17] . h ttp :/ /en .wi kip ed ia .or g/w iki /S IMD . [6 ] Hua ng SB, Zh en g QL, Gu o LW. S IMD com pi ler op ti mi zat ion b y s ele ct in g s in gle or dou ble wor d m ode for cl us te red VLI W DS P . Jou rn al of Co mp ut er App li cat io ns , 201 5,3 5 (8): 23 71 -23 74 . [7 ] Wan g H, Hu an g G H, W an g XQ. Re sea rch an d Im ple men t ati on of Pr opa ga gti on Clu st er A lgo rit h m Bas ed on BW DSP1 0 0. Chin a Int egr at ed Ci rc ult , 201 4 , (1 83 ): 26 - 27. [8 ] Ji an g J , Wan g C , Wei HM . An Opt imi sa tion Str ate gy For Loca l R egi st er Al loc at ion . Comp u ter Ap pli ca ti on s a nd Soft war e, 20 13 , 30 (12 ): 2 16-2 17. [9 ] F red C. Ch ow, J oh n L. Hen ni s sy. The pr ior it y-Ba se d C olor in g Ap pr oac h t o Re gis te r All oc ati on . AC M Tr an s. on P rogr am min g Lang ua ges an d Sys te ms , 1 990 ,12 (4 ):50 1 - 536 [1 0] C. Wi mme r, M. Fra nz . Li ne ar s can reg is te r a lloca ti on on s sa fo rm. In Pro ce ed in gs o f th e IE EE/A CM Inte rn at ion al S ymp osi u m on Cod e Ge ner ati on an d Opt imi za ti on, 201 0: 170 – 1 79 . [1 1] Su br at o Ku ma r De. De sig n of a re ta rg et abl e c omp il er for di gi ta l s ig na l p roc es sor s. Ge orgi a in st itu te of t ech no logy, 2 002 :6 5 - 71 刘彬彬 郑启龙 : 分簇 V LIW DSP 上特殊指令实现之乘法累加指令 7 附 中 文 参 考 文 献 : [ 1] CE TC3 8. BWDS P 软件用户手册 [R]. 合肥 : 中国电子科技集团第三十八研究所 , 20 11 : 18 1- 19 7. [2 ] CET C3 8. BWDS P 硬件用户手册 [R]. 合肥 : 中国电子科技集团第三十八研究所 , 201 1 :1- 2. [6 ] 黄胜兵 , 郑启龙 , 郭连伟 . 分簇 V LIW DS P 上支持单双字模式选择的 S IMD 编译优化 , 计算机应用 ,2 01 5,3 5 (8): 237 1-2 3 74. [7 ] 王昊 , 黄光红 , 王向前 . 基于 BW DSP 100 的传播分簇算法研究与实现 . 中国集成电路 ,2 014 ,(1 83 ): 26 - 27. [8 ] 姜军 , 王超 , 尉红梅 . 一种局部寄存器分配的优化策略 . 计算机应用与软件 , 20 13,3 0 (12 ):2 16 - 217.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment