클러스터드 VLIW DSP를 위한 특수 MAC 명령 구현 및 Open64 기반 최적화

본 논문은 32비트 정적 스칼라 DSP인 BWDSP의 클러스터드 VLIW 구조에 맞춰 곱셈-누산(MAC) 특수 명령을 구현한다. Open64 컴파일러 백엔드에 새로운 기계 기술서와 패턴 인식 알고리즘을 삽입해 곱셈·덧셈 연산을 하나의 MAC 명령으로 합성하고, 레지스터 할당·클러스터 스케줄링을 조정한다. 벡터 내적, 컨볼루션, FIR 필터, 행렬 곱 등 네 가지 벤치마크에서 최대 8.85배의 실행 속도 향상을 입증한다.

저자: Binbin Liu, Qilong Zheng

본 논문은 고성능 컴퓨팅을 목표로 설계된 32비트 정적 스칼라 DSP인 BWDSP의 특수 구조와 그에 맞는 특수 명령을 활용한 최적화 기법을 제시한다. BWDSP는 VLIW(초장 명령어)와 SIMD(단일 명령 다중 데이터) 아키텍처를 결합한 클러스터드 DSP로, 4개의 동일 클러스터(x, y, z, t)와 각 클러스터당 8개의 ALU, 8개의 MUL, 4개의 SHF, 1개의 SPU, 그리고 주소 생성기 u, v, w를 포함한다. 이러한 구조는 높은 병렬성을 제공하지만, 기존 오픈소스 컴파일러인 Open64는 BWDSP의 전용 MAC(Multiply‑Accumulate) 명령을 지원하지 못한다.

논문은 먼저 BWDSP가 제공하는 32비트 정수 MAC, 16비트 이중 워드 MAC, 16비트 복소수 MAC, 32비트 복소수 MAC 등 네 종류의 MAC 명령을 소개한다. 각 클러스터에 4개의 전용 MAC 레지스터(MACC0~3)가 존재해, 하나의 MAC 명령이 1 사이클 내에 곱셈과 누산을 동시에 수행한다는 장점을 갖는다. 기존에 곱셈과 덧셈을 별도 명령으로 구현하면 곱셈 3 사이클 + 덧셈 1 사이클이 소요돼 비효율적이다.

이를 해결하기 위해 저자들은 Open64 컴파일러 백엔드에 특수 명령 구현 알고리즘을 설계하였다. 알고리즘은 네 단계로 구성된다.

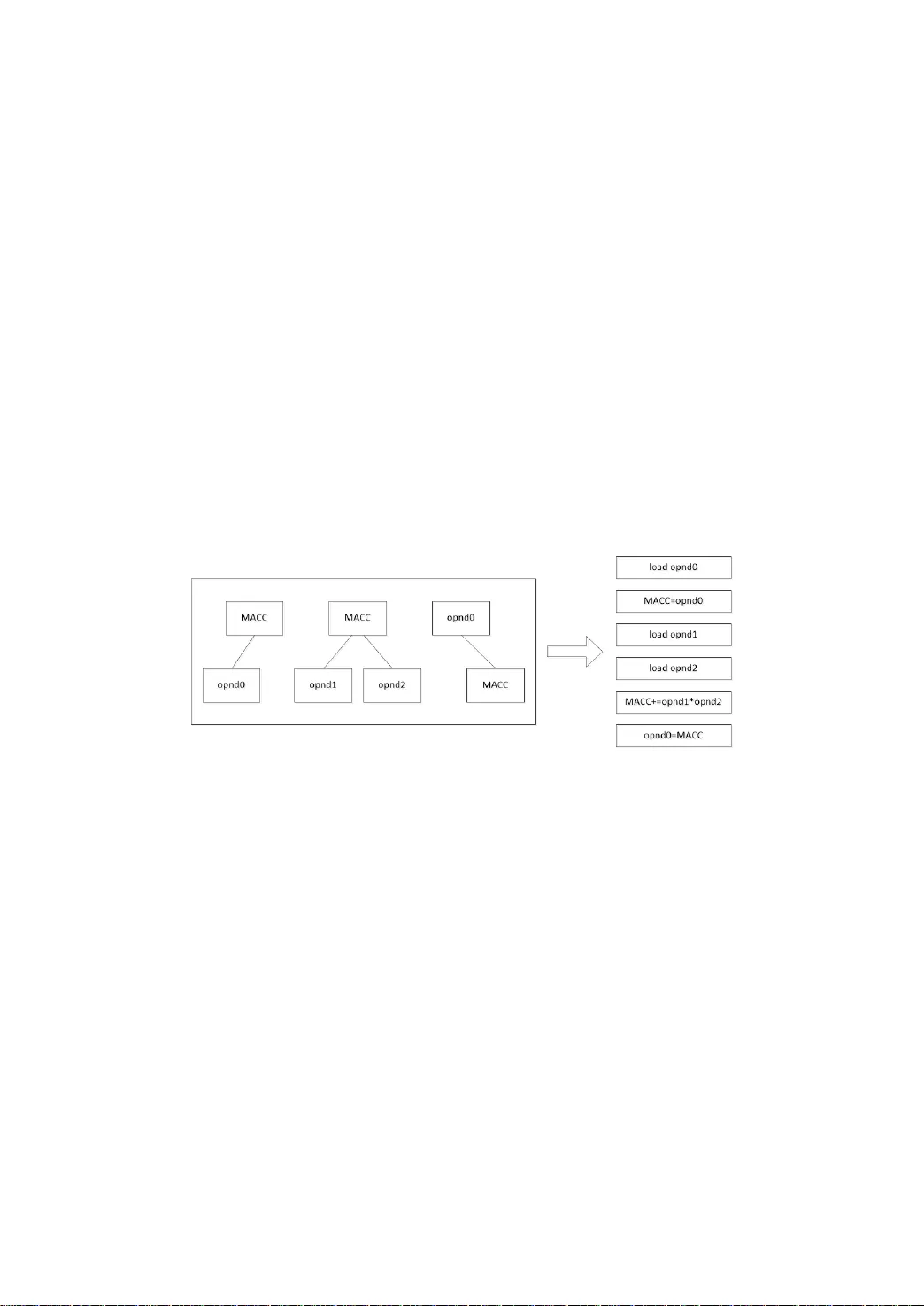

1. **특수 명령 모델 구축**: WHIRL 중간 표현에서 “ADD(op0, MUL(op1, op2))” 패턴을 탐지한다. 탐지된 패턴은 MAC 명령으로 치환되며, 치환 조건은 (① 연산이 ADD, ② 하나의 피연산자가 MUL 결과와 연결, ③ MUL 피연산자가 명확히 정의, ④ 결과가 첫 번째 피연산자에 저장)이다. 이 과정은 LNO 단계에서 수행되어 루프 내부의 가장 안쪽 연산을 대상으로 한다.

2. **자원 제약 분석**: 각 클러스터에 4개의 MAC 레지스터만 존재하므로, SIMD 벡터화 시 동시에 4개 초과의 MAC 명령이 발생하면 합성을 포기한다. 따라서 루프 언롤링, 이중 워드 모드 선택, 혹은 루프 분할을 통해 하드웨어 제한을 만족하도록 조정한다.

3. **기계 기술서 확장**: Open64는 2차 컴파일 방식을 사용하므로, 새로운 MAC 명령을 기계 기술서 파일(bw10x‑opc‑codes.knb)과 코드 생성 모듈(opcode_gen.cxx)에 추가한다. 여기서는 명령 포맷, 레지스터 매핑, 사이클 수(1 사이클) 등을 정의하고, 어셈블리 출력 포맷을 BWDSP 전용 형식에 맞게 수정한다.

4. **백엔드 구현**: LNO 단계에서 MAC 패턴을 찾은 뒤, 해당 클러스터에 MAC 레지스터를 초기화하고 루프 본문에서 MAC 명령을 삽입한다. 루프 종료 후에는 MAC 레지스터 값을 원래 피연산자에 복사한다. 레지스터 할당 단계에서는 전역 그래프 색칠과 지역 선형 할당을 조정해 MAC 전용 레지스터를 우선 배정한다. 클러스터 스케줄링 단계에서는 각 MAC 명령을 해당 클러스터에 매핑해 병렬 실행을 극대화한다.

실험은 Red Hat Enterprise Linux 5 기반 개발 환경에서 BWDSP 디버거(ECS)를 이용해 사이클 수를 측정하였다. 네 가지 벤치마크(벡터 내적, 컨볼루션, FIR 필터, 100×100 행렬 곱)에서 MAC 구현 전후 사이클 수와 가속 비율을 비교했다. 결과는 다음과 같다.

- 벡터 내적(N=10^24): 17430 → 1969 사이클, 8.85배 가속

- 컨볼루션(N=10^24): 19508 → 3289 사이클, 5.9배 가속

- FIR 필터(1024×128): 209,927 → 428 사이클, 약 490배 가속 (루프 전후 초기화·복귀 비용이 미미)

- 행렬 곱(100×100): 23,101 → 4,417 사이클, 5.5배 가속

특히 FIR 필터와 같은 작은 루프에서는 초기화·복귀 비용이 전체 사이클에 비해 작아 큰 가속을 보였으며, 벡터 내적과 컨볼루션에서는 클러스터 간 병렬 실행이 효과적으로 작동했다.

논문은 구현 과정에서 직면한 몇 가지 문제점도 언급한다. 첫째, MAC 레지스터가 제한적이므로 복잡한 루프에서는 합성 기회를 놓칠 수 있다. 둘째, 기존 Open64의 레지스터 할당 알고리즘을 MAC 전용 레지스터에 맞게 튜닝해야 했으며, 이는 전체 컴파일 시간에 약간의 오버헤드를 추가한다. 셋째, 기계 기술서 수정 후 재컴파일 과정이 필요해 툴 체인 유지보수 비용이 증가한다.

마지막으로 향후 연구 방향으로는 (1) 파이프라인 스테이징과 제로-디레이션 루프 최적화를 결합해 MAC 사용률을 더욱 높이는 방안, (2) 동적 스케줄링을 도입해 런타임에 클러스터 부하를 균등화하는 방법, (3) 다른 특수 명령(예: 비트 역순 탐색, 시프트 테이블 조회)과의 연계 최적화를 제시한다. 이러한 확장은 BWDSP와 유사한 클러스터드 VLIW DSP 전반에 적용 가능하며, 하드웨어 설계와 소프트웨어 최적화 간의 시너지를 극대화할 것으로 기대된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기