이진신경망을 활용한 손글씨 숫자 인식 FPGA 가속기

📝 원문 정보

- Title: Binary Neural Network Implementation for Handwritten Digit Recognition on FPGA

- ArXiv ID: 2512.19304

- 발행일: 2025-12-22

- 저자: Emir Devlet Ertörer, Cem Ünsalan

📝 초록 (Abstract)

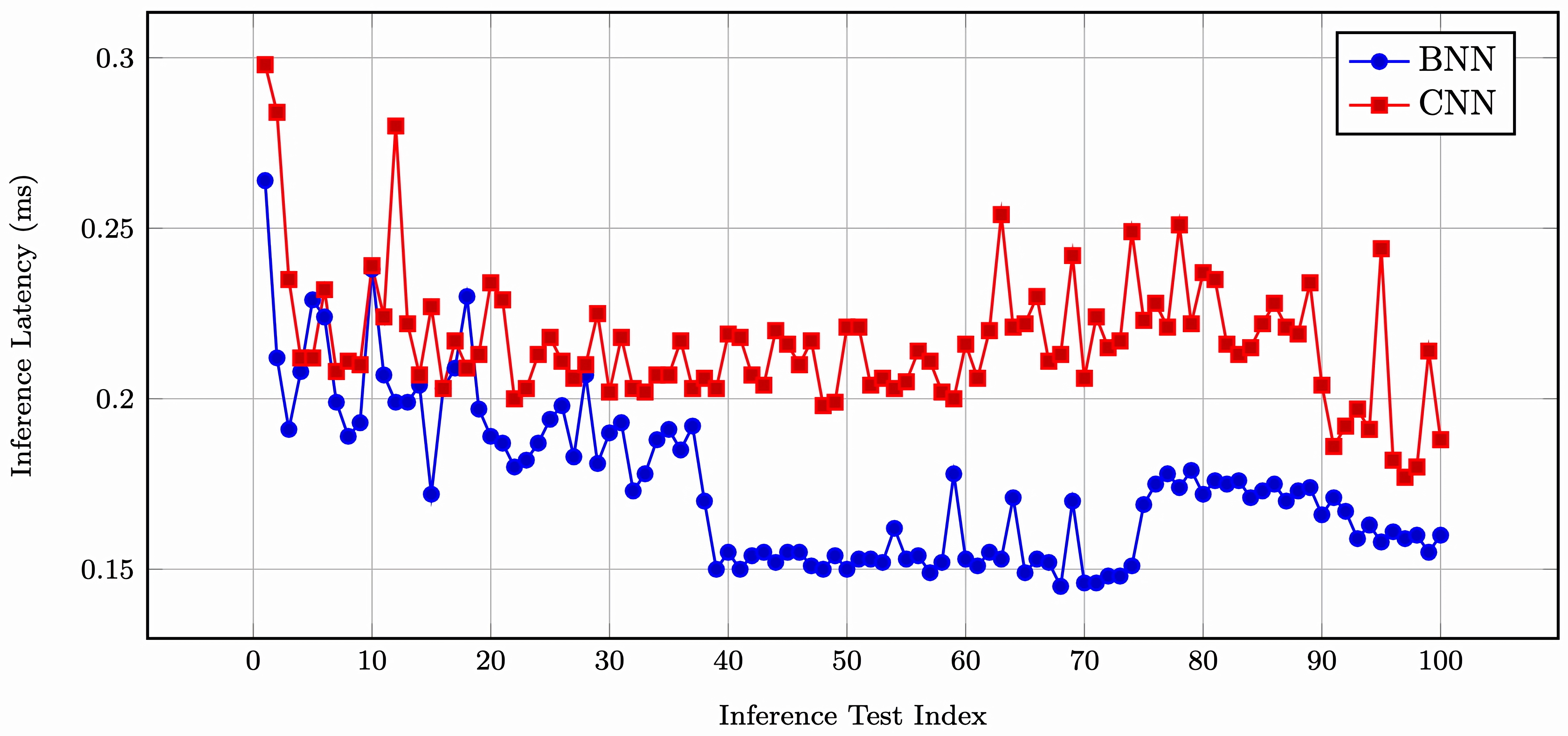

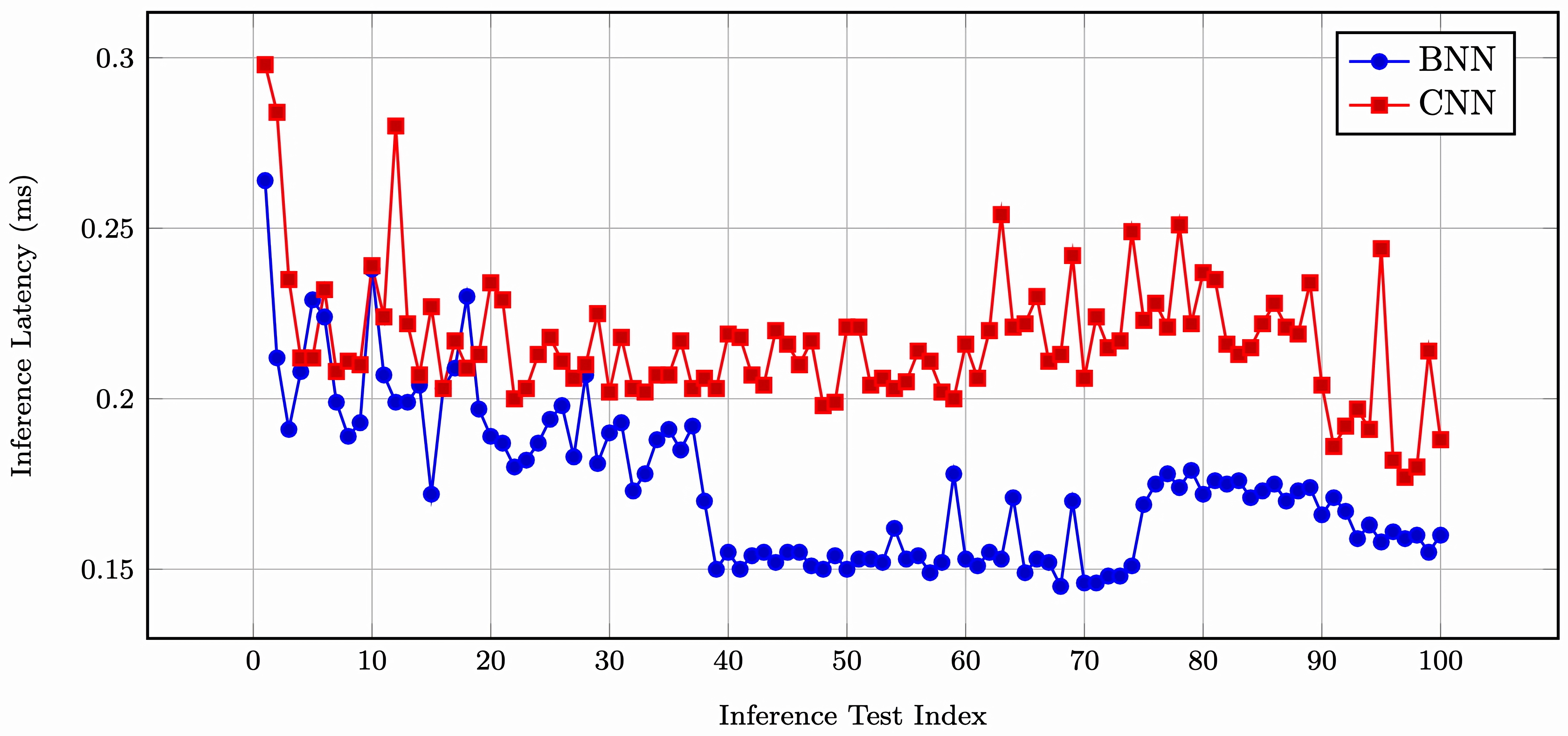

이진 신경망은 부동소수점 연산을 비트 논리로 대체하여 저전력, 고속 추론을 제공하는 유망한 해결책입니다. 이 연구에서는 Xilinx Artix-7 FPGA를 타겟으로 하는 손글씨 숫자 인식용 완전히 커스텀 이진 신경망 추론 가속기를 제시합니다. 이 설계는 고수준 합성 도구 없이 Verilog로 완전하게 구현되었으며, 80 MHz에서 실시간 분류를 달성하고 낮은 전력 소비와 예측 가능한 타이밍을 제공합니다. 시뮬레이션 결과는 MNIST 테스트 세트에서 84%의 정확도를 보여주며, 임베디드 시스템에서 이진 신경망 배포에 대한 수동 HDL 설계의 장점을 강조합니다.💡 논문 핵심 해설 (Deep Analysis)

MNIST 데이터셋에 대한 시뮬레이션 결과에서는 84%의 정확도를 기록하였습니다. 이는 BNN가 손글씨 숫자 인식에 적합함을 입증하는 결과입니다. 또한, 수작업 HDL 설계 방식은 투명성과 효율성을 높이고, 임베디드 시스템에서의 유연한 배포를 가능하게 합니다.

논문에서는 프로젝트의 재현 가능성과 미래 개발을 위해 훈련 스크립트와 Verilog 소스 코드가 공개되어 있습니다. 이를 통해 연구자들은 이진신경망 기반 가속기 설계에 대한 더 깊은 이해를 얻고, 다양한 응용 분야에서의 활용 가능성을 탐색할 수 있을 것입니다.

📄 논문 본문 발췌 (Excerpt)

📸 추가 이미지 갤러리

Reference

이 글은 ArXiv의 공개 자료를 바탕으로 AI가 자동 번역 및 요약한 내용입니다.

저작권은 원저자에게 있으며, 인류 지식 발전에 기여한 연구자분들께 감사드립니다.