가속기 설계 언어 컴파일러 성능 프로파일링 도구 Petal

📝 원문 정보

- Title: Understanding Accelerator Compilers via Performance Profiling

- ArXiv ID: 2511.19764

- 발행일: 2025-11-24

- 저자: Ayaka Yorihiro, Griffin Berlstein, Pedro Pontes García, Kevin Laeufer, Adrian Sampson

📝 초록 (Abstract)

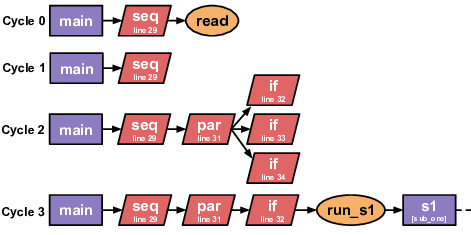

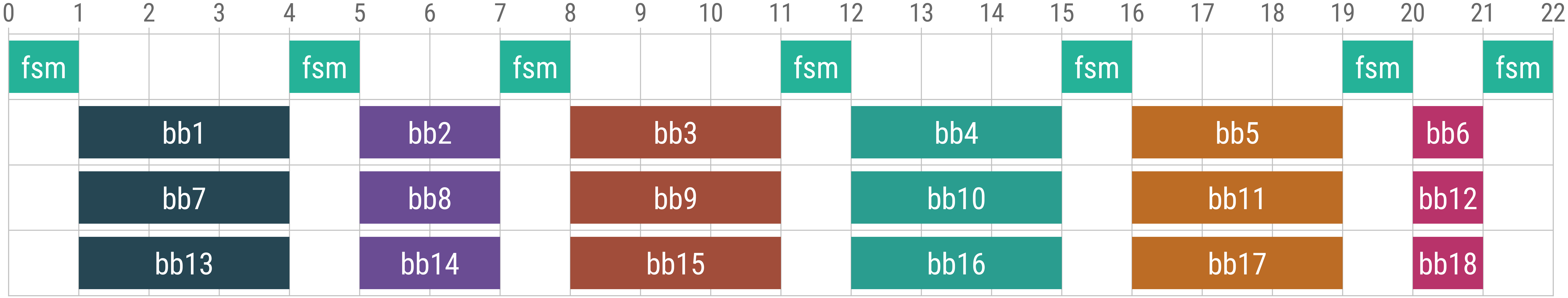

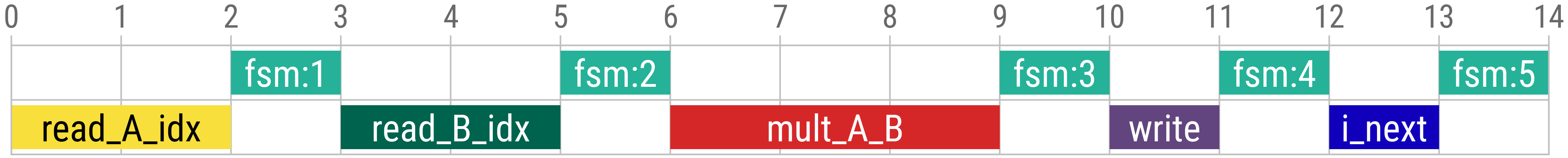

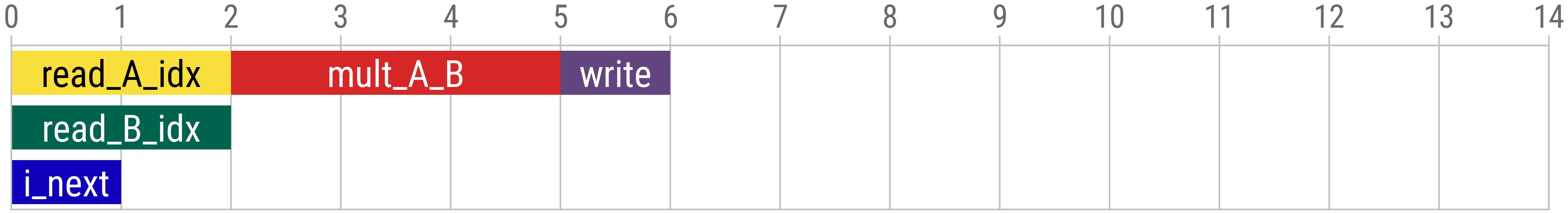

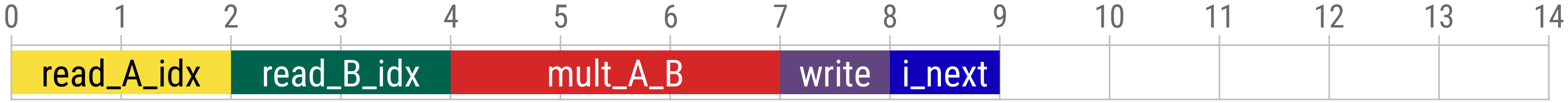

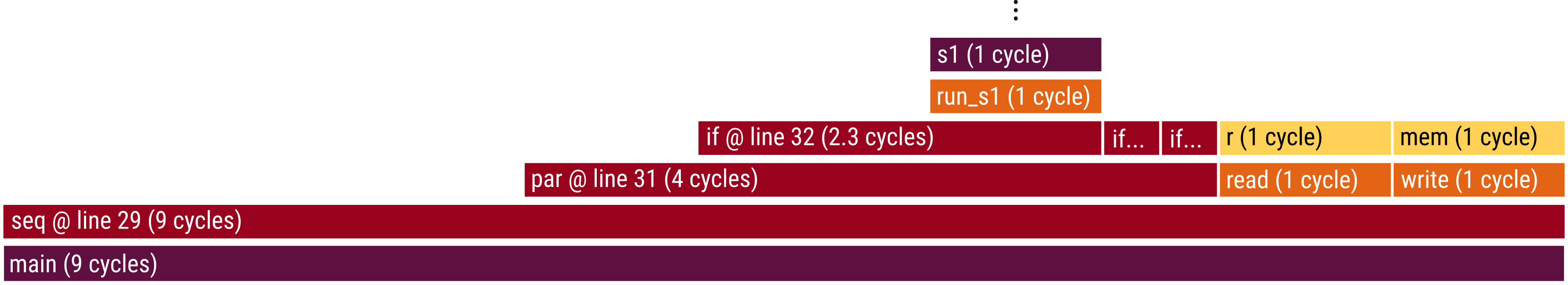

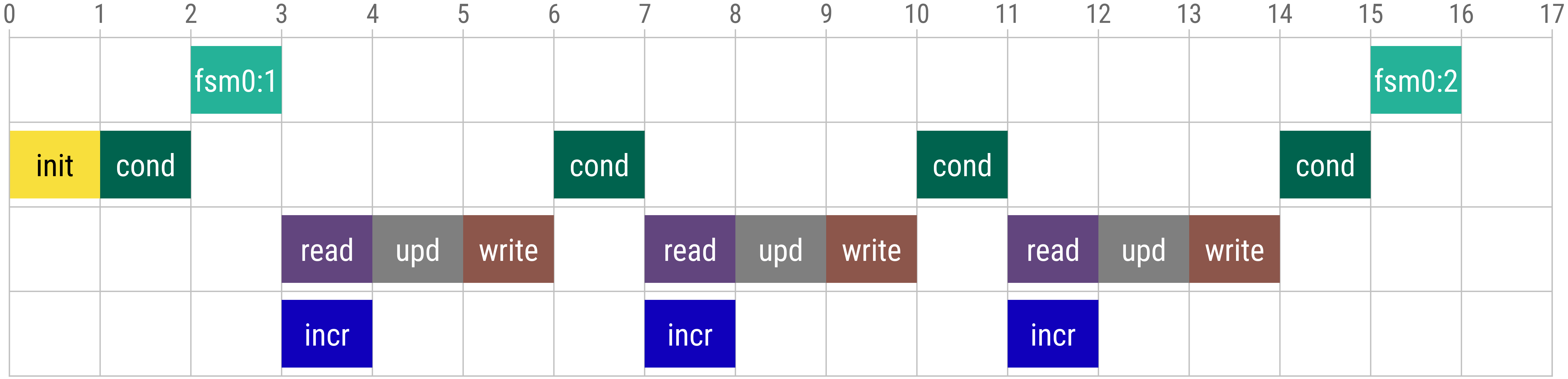

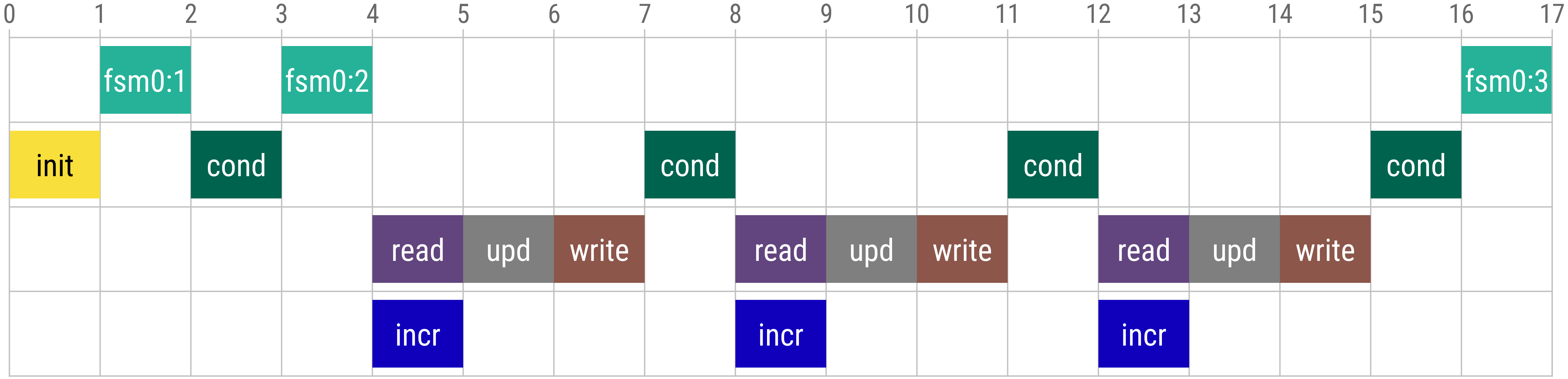

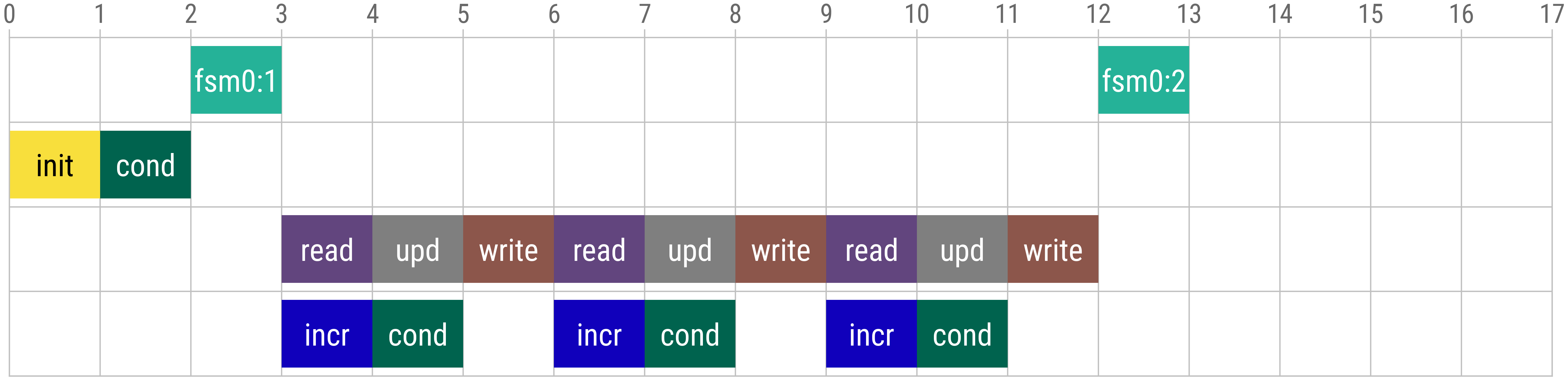

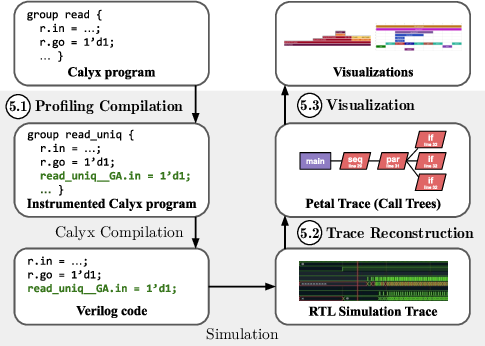

가속기 설계 언어(ADL)는 하드웨어 유닛으로 컴파일되는 고수준 언어로, 도메인 전문가가 효율적인 애플리케이션 전용 하드웨어를 빠르게 설계하도록 돕는다. ADL 컴파일러는 데이터 경로를 최적화하고 소프트웨어와 유사한 제어 흐름 구문을 제어 경로로 변환한다. 이러한 컴파일러는 고수준 의미와 사이클 수준 스케줄 사이의 넓은 의미 격차를 메워야 하며, 회로 최적화를 위해 복잡한 휴리스틱에 의존하기 때문에 필연적으로 복잡하고 예측이 어려운 특성을 가진다. 결과적인 성능은 제어하기 힘들어, 생성된 하드웨어의 성능 문제를 찾고 해결하기 위해 추측에 의존해야 한다. 우리는 ADL 컴파일러가 완벽해질 수 없으며, 일정 수준의 성능 예측 불가능성은 문제 자체에 내재한다고 가정한다. 컴파일러 완전성 대신, 우리는 ADL 프로그래머에게 컴파일러의 결정이 성능에 미치는 영향을 통찰시켜 주는 컴파일러 이해 도구가 필요하다고 주장한다. 본 논문에서는 Calyx 중간 언어(IL)를 위한 사이클 수준 프로파일러인 Petal을 소개한다. Petar는 Calyx 코드에 프로브를 삽입하고 레지스터‑전달‑레벨 시뮬레이션에서 얻은 트레이스를 분석한다. 트레이스의 이벤트를 Calyx 코드의 고수준 제어 구문에 매핑하여 각 구문이 활성화된 클록 사이클을 추적한다. 사례 연구를 통해 Petal의 사이클 수준 프로파일이 기존 가속기 설계의 성능 문제를 식별할 수 있음을 보여준다. 또한 이러한 통찰이 컴파일러가 자동으로 수행하지 못한 최적화를 유도할 수 있음을 입증했으며, 한 애플리케이션에서는 전체 사이클을 46.9 % 감소시켰다.💡 논문 핵심 해설 (Deep Analysis)

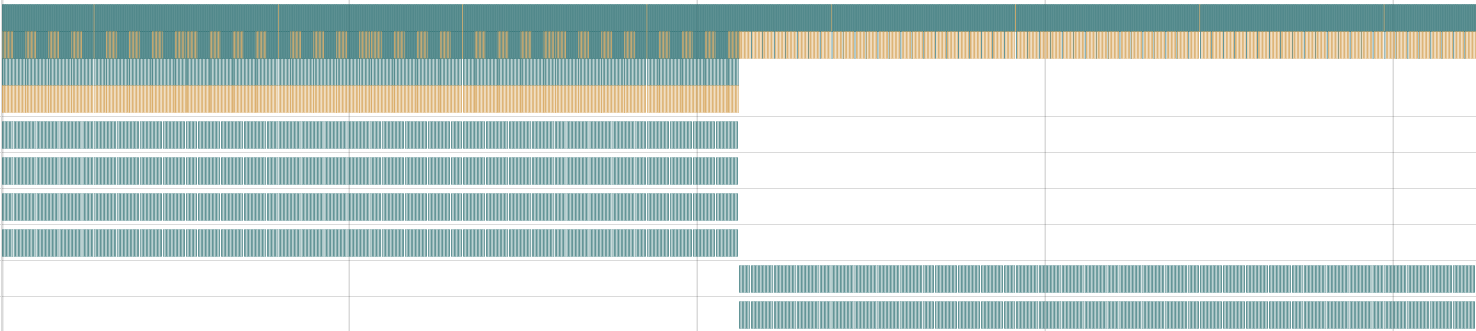

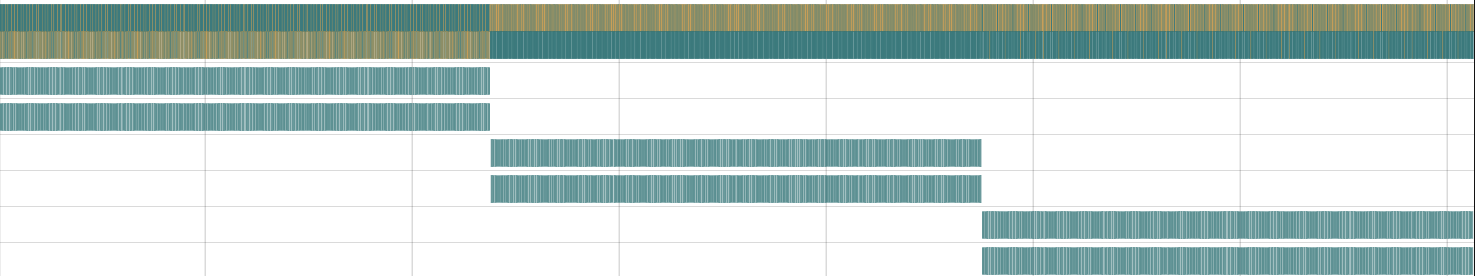

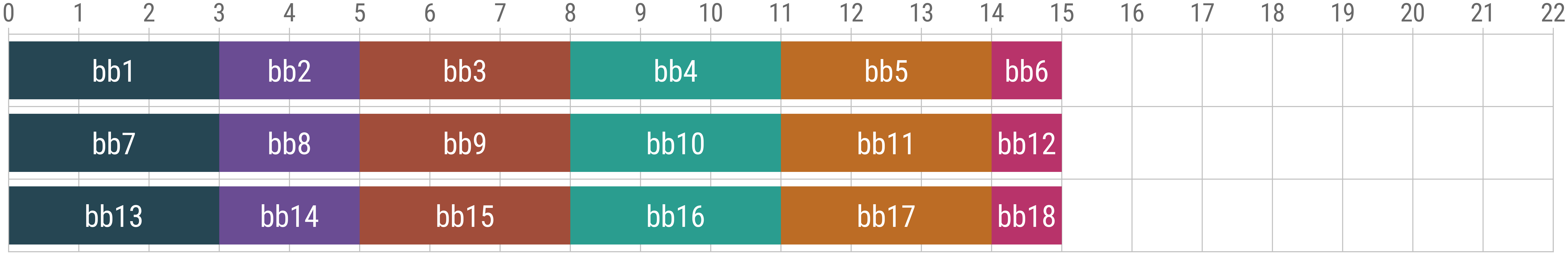

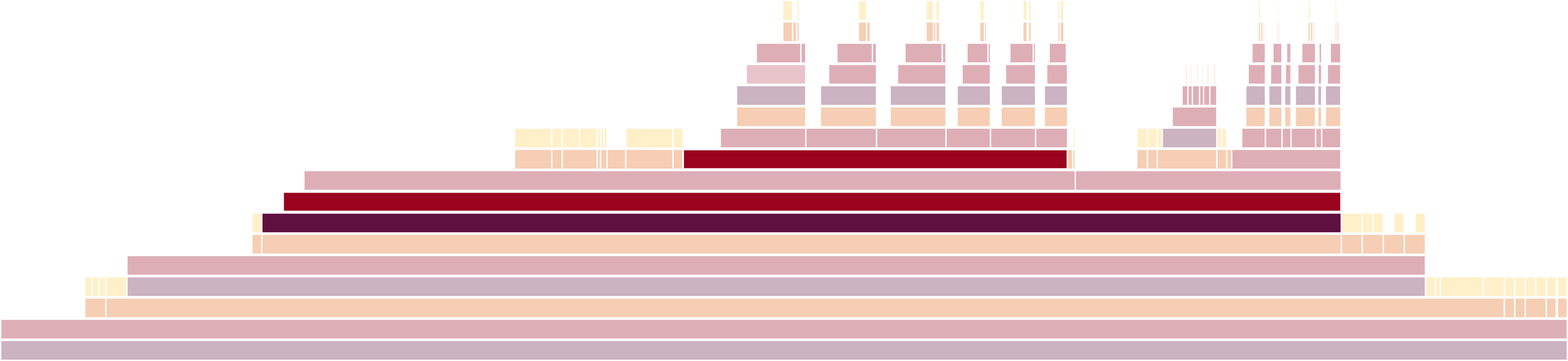

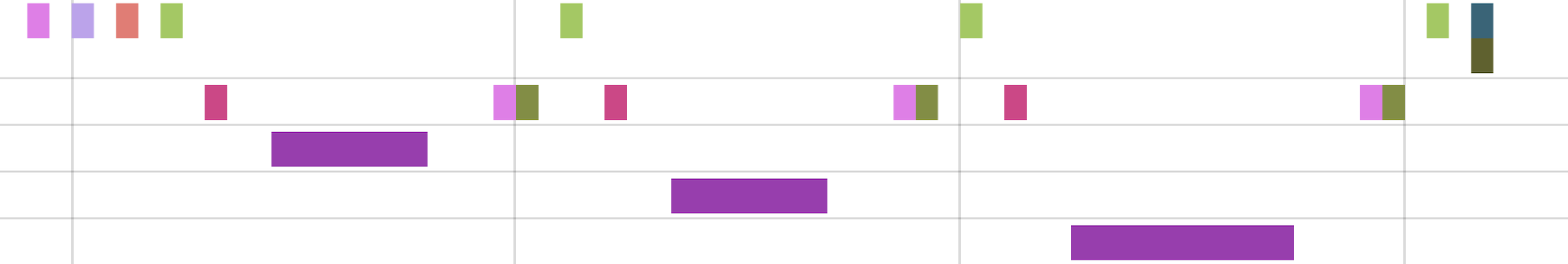

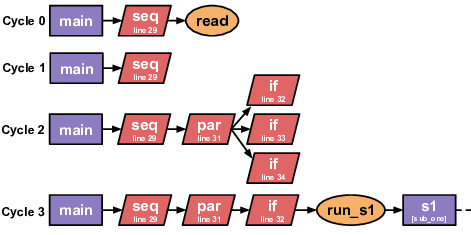

Petal은 이러한 문제를 해결하기 위해 두 가지 핵심 메커니즘을 도입한다. 첫째, Calyx IL에 삽입된 프로브는 시뮬레이션 단계에서 각 연산·제어 구문의 실행 시점을 정확히 기록한다. 둘째, 수집된 트레이스를 Calyx 소스 코드와 매핑함으로써, 고수준 제어 구조(예: 루프, 조건문, 파이프라인 단계)가 실제 하드웨어에서 차지하는 사이클 수를 정량화한다. 이 매핑 과정은 단순히 전체 사이클을 보고하는 기존 프로파일러와 달리, 성능 병목이 발생하는 구문을 직접 식별할 수 있게 한다.

논문에 제시된 사례 연구는 Petal이 실제 설계 흐름에 어떻게 적용되는지를 보여준다. 예를 들어, 특정 루프 구조가 예상보다 많은 사이클을 소비하는 이유가 컴파일러가 루프 언롤링을 충분히 수행하지 못했기 때문이라는 사실을 트레이스에서 명확히 드러냈다. 설계자는 이 정보를 바탕으로 루프 바디를 재구성하거나, 메모리 접근 패턴을 재조정하는 등 수동 최적화를 적용했으며, 결과적으로 전체 실행 시간의 46.9 %를 절감했다. 이는 컴파일러가 자동으로 달성하지 못한 최적화 여지를 프로파일링 도구가 효과적으로 밝혀낼 수 있음을 증명한다.

또한, Petal은 Calyx와 같은 중간 언어 기반 설계 흐름에 특화되어 있기 때문에, 다른 ADL 혹은 고수준 합성 프레임워크에도 확장 가능성이 크다. 향후 연구에서는 프로파일링 데이터를 기반으로 자동 리팩터링 제안을 하는 피드백 루프를 구축하거나, 머신러닝 모델을 활용해 컴파일러 휴리스틱을 동적으로 조정하는 방안이 기대된다. 전반적으로, 이 논문은 하드웨어 컴파일러의 블랙박스성을 해소하고, 설계자가 성능을 직관적으로 이해·조정할 수 있는 도구적 기반을 제공한다는 점에서 큰 의의를 가진다.

📄 논문 본문 발췌 (Excerpt)

📸 추가 이미지 갤러리