마이크로아키텍처 기반 멜트다운·스펙터 방어 메커니즘

📝 원문 정보

- Title: Pre-cache: A Microarchitectural Solution to prevent Meltdown and Spectre

- ArXiv ID: 2511.17726

- 발행일: 2025-11-21

- 저자: Subhash Sethumurugan, Hari Cherupalli, Kangjie Lu, John Sartori

📝 초록 (Abstract)

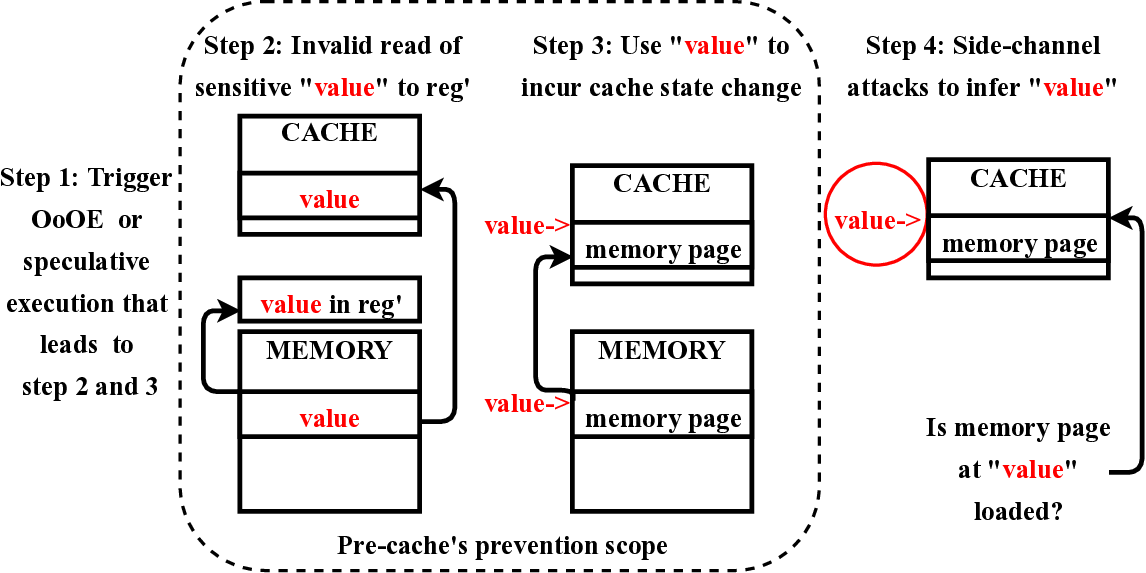

최근 연구에 따르면 현대 프로세서가 성능 향상을 위해 사용하는 순서 뒤섞기와 사전 실행 메커니즘이 치명적인 공격에 노출된다는 것이 밝혀졌다. 멜트다운과 스펙터라는 공격은 이러한 마이크로아키텍처의 성능 강화 기능이 남기는 부작용을 이용해 사이드 채널을 통해 비밀 데이터를 유출한다. 기존 구현은 캐시 기반 사이드 채널을 주로 이용하는데, 이는 가장 잡음이 적은 경로이기 때문이다. 일부 소프트웨어 패치는 이러한 공격을 완화하려 시도했지만, 이는 임시방편에 불과하고 취약점의 근본 원인을 해결하지 못한다. 또한 성능 저하가 최대 30%에 달한다. 본 논문에서는 멜트다운·스펙터가 악용하는 취약점을 직접 차단하는 마이크로아키텍처 수준의 해결책을 제시한다. 제안된 방법은 플러시된 명령이 캐시에 데이터를 노출하지 못하도록 막으며, 동일한 원리를 다른 메모리 구조에도 적용해 해당 구조를 이용한 변종 공격도 방어할 수 있다. 또한 사전 실행 및 순서 뒤섞기 부작용을 이용한 두 가지 새로운 변종 공격을 정의하고, 우리의 솔루션이 이를 효과적으로 차단함을 보인다. 평가 결과, 제안된 마이크로아키텍처 방어는 안전한 사전 실행과 순서 뒤섞기를 복원함과 동시에 대부분의 애플리케이션에서 큰 성능 저하 없이 낮은 오버헤드를 유지한다.💡 논문 핵심 해설 (Deep Analysis)

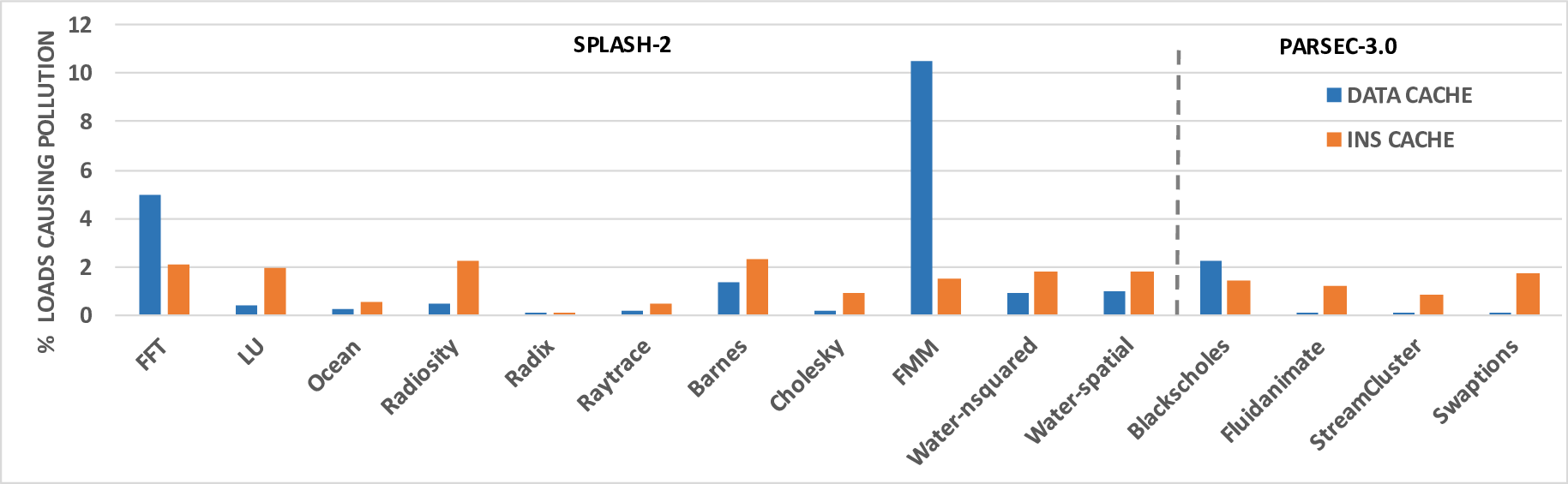

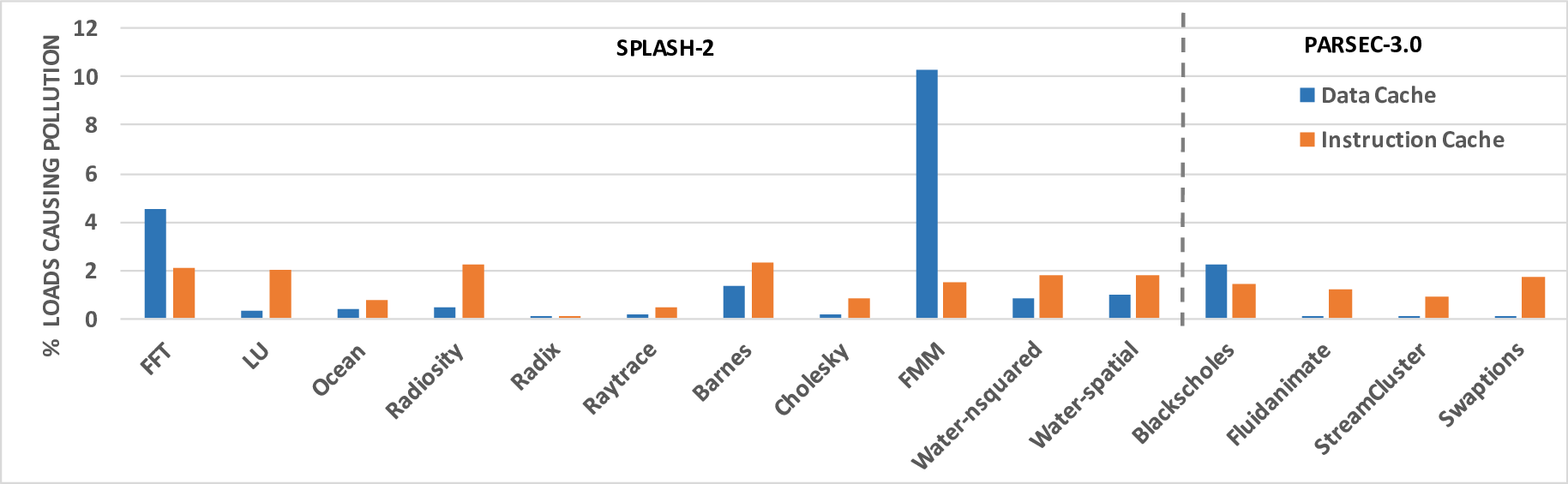

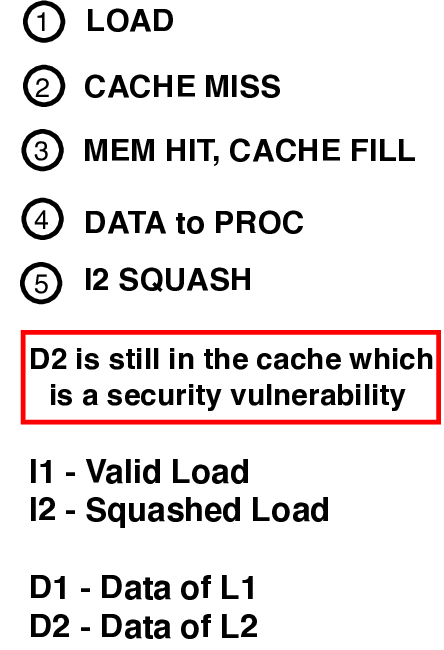

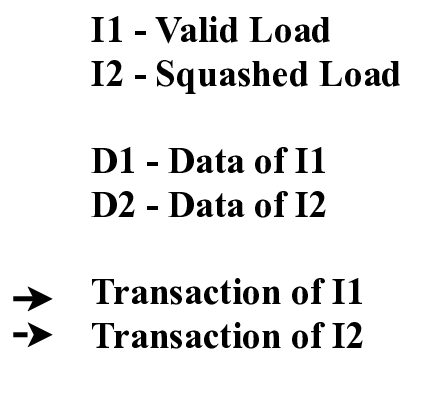

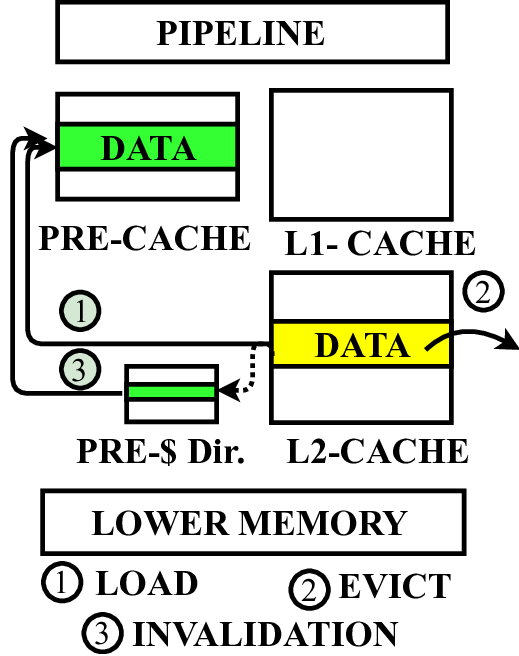

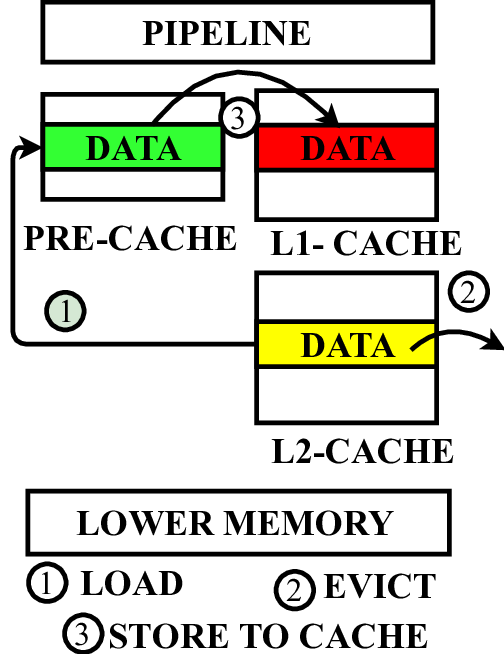

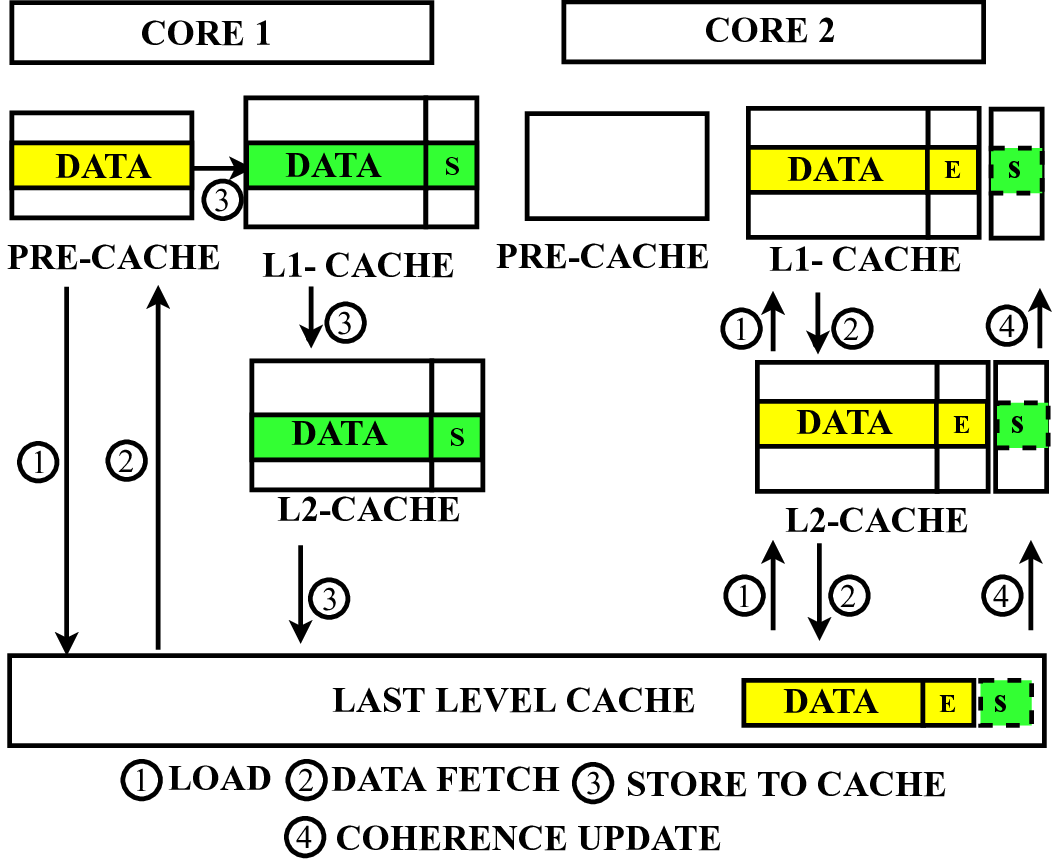

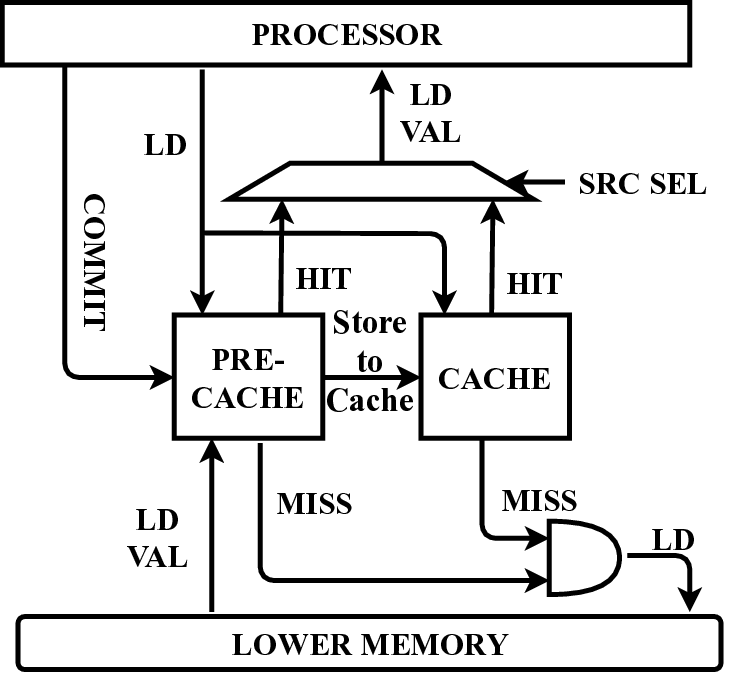

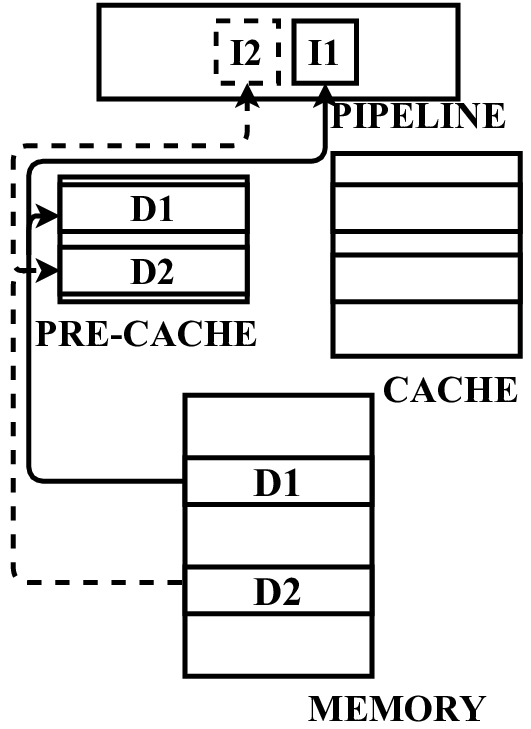

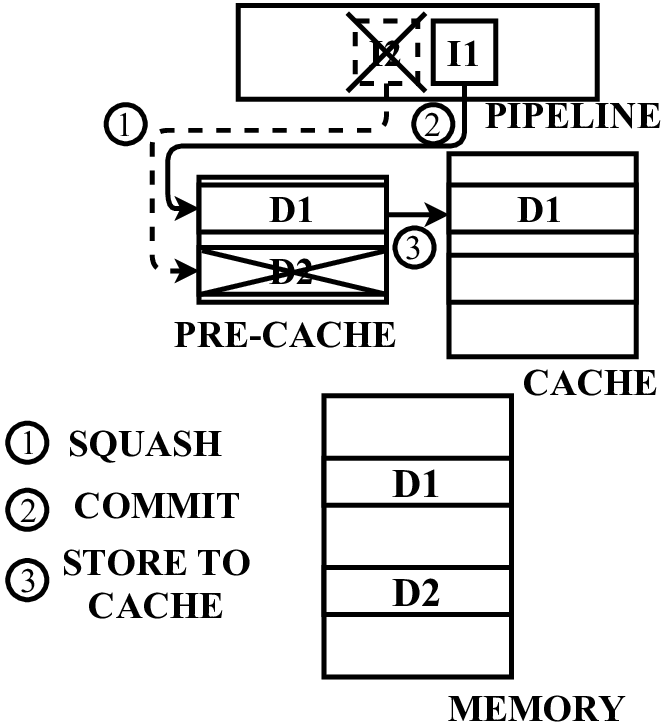

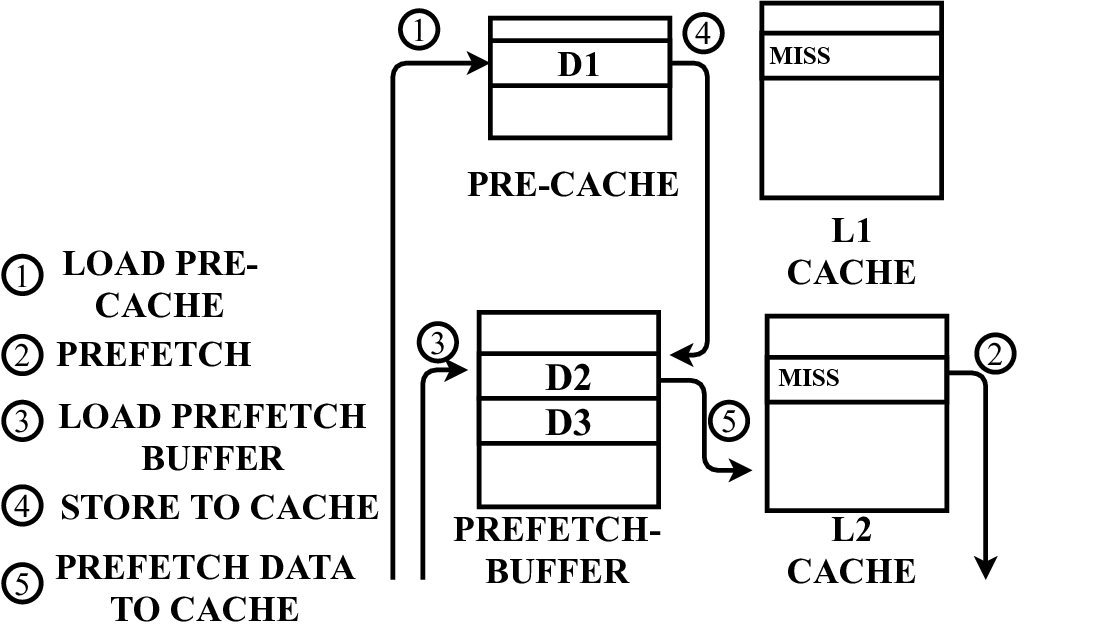

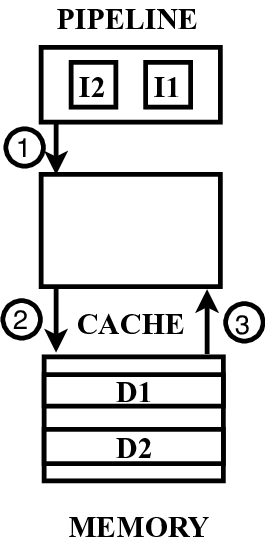

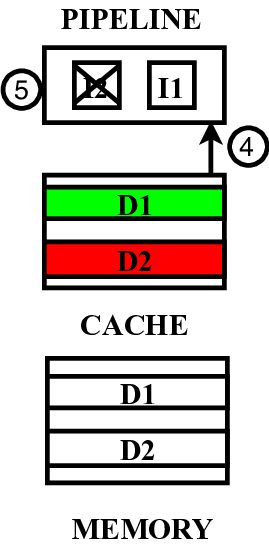

본 논문이 제안하는 마이크로아키텍처 기반 방어는 “플러시된 명령이 캐시를 오염시키지 못하도록 하는” 하드웨어 로직을 추가한다. 구체적으로, 명령이 추측 실행 단계에서 롤백될 경우 해당 명령이 접근한 메모리 주소에 대한 캐시 라인 업데이트를 억제하거나, 라인 상태를 ‘무효화(invalidate)’ 상태로 전환한다. 이렇게 하면 추측 실행이 실패하더라도 캐시에는 어떠한 데이터도 남지 않아 사이드 채널이 사라진다. 이 메커니즘은 캐시뿐 아니라 TLB, 분기 예측 버퍼 등 다른 마이크로아키텍처 구조에도 동일하게 적용 가능하므로, 구조적 변종 공격까지 포괄적으로 방어한다.

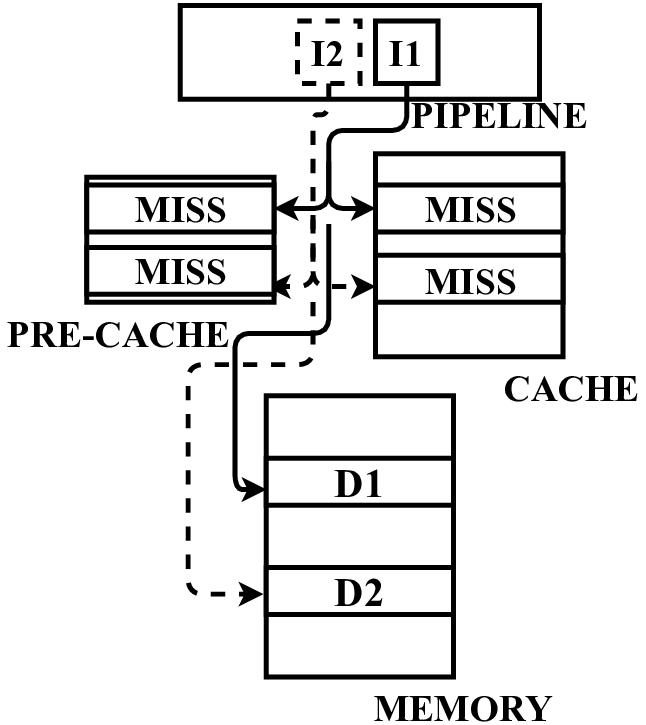

또한 저자들은 기존 공격을 변형한 두 가지 새로운 변종을 설계하였다. 첫 번째는 추측 실행 중 발생한 메모리 의존성을 이용해 비밀 데이터를 직접 레지스터에 복사한 뒤, 레지스터‑캐시 전파 과정을 통해 정보를 유출하는 방식이다. 두 번째는 순서 뒤섞기 파이프라인에서 발생하는 ‘재정렬 버퍼(ROB)’의 상태 변화를 관찰해 비밀 데이터를 추론하는 기법이다. 제안된 하드웨어 방어는 이러한 경로에서도 메모리·레지스터 간의 부수 효과를 차단함으로써 성공을 저지한다.

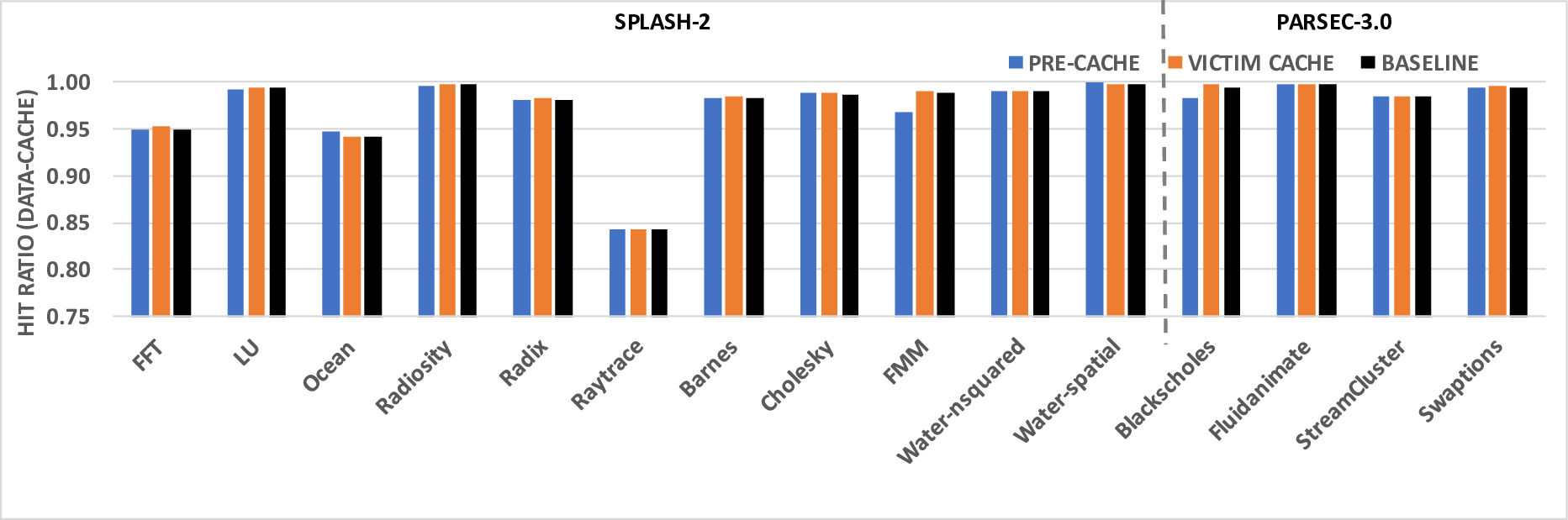

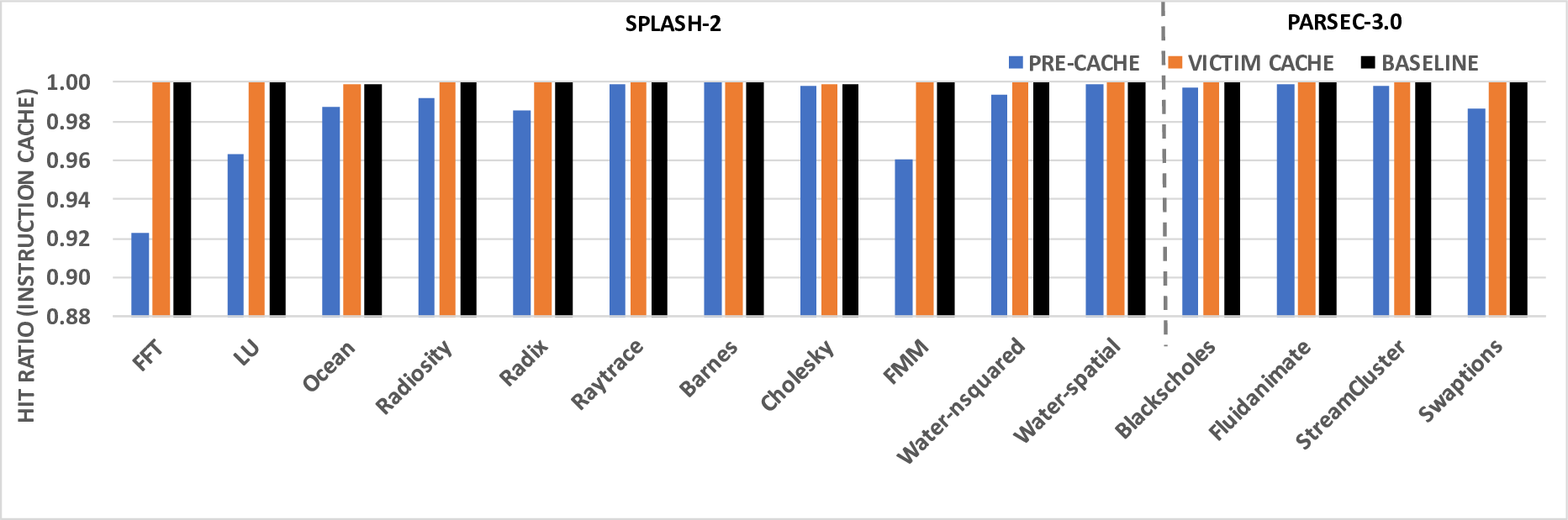

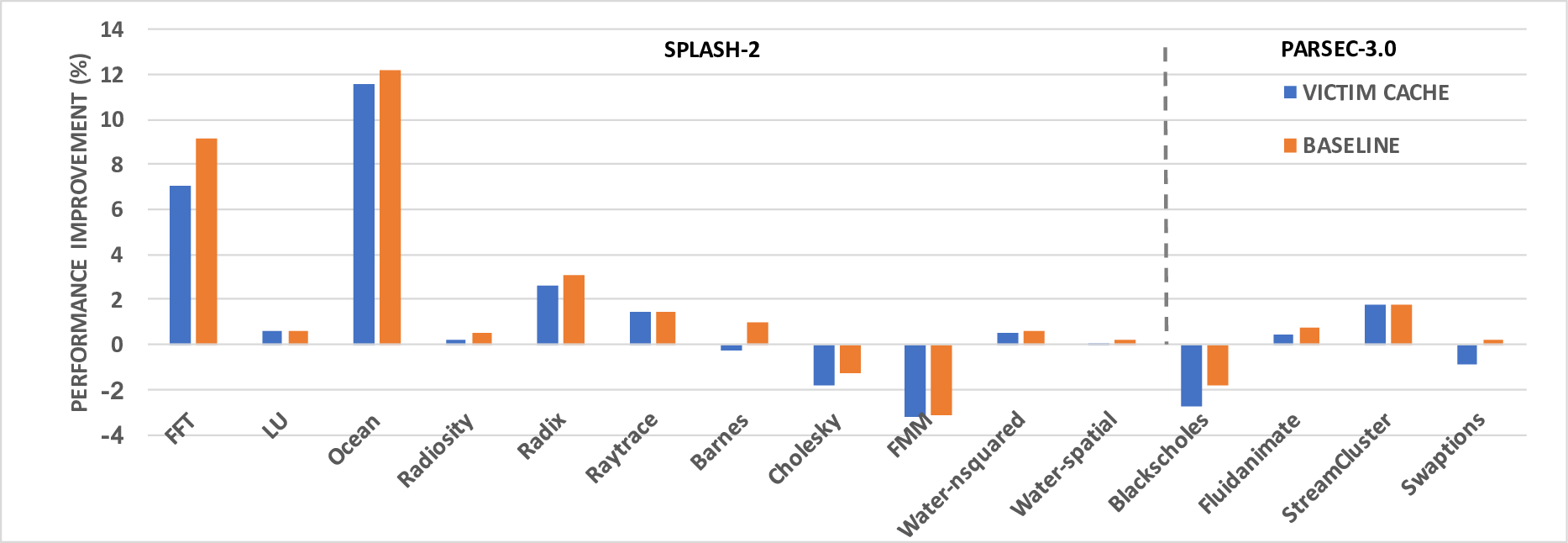

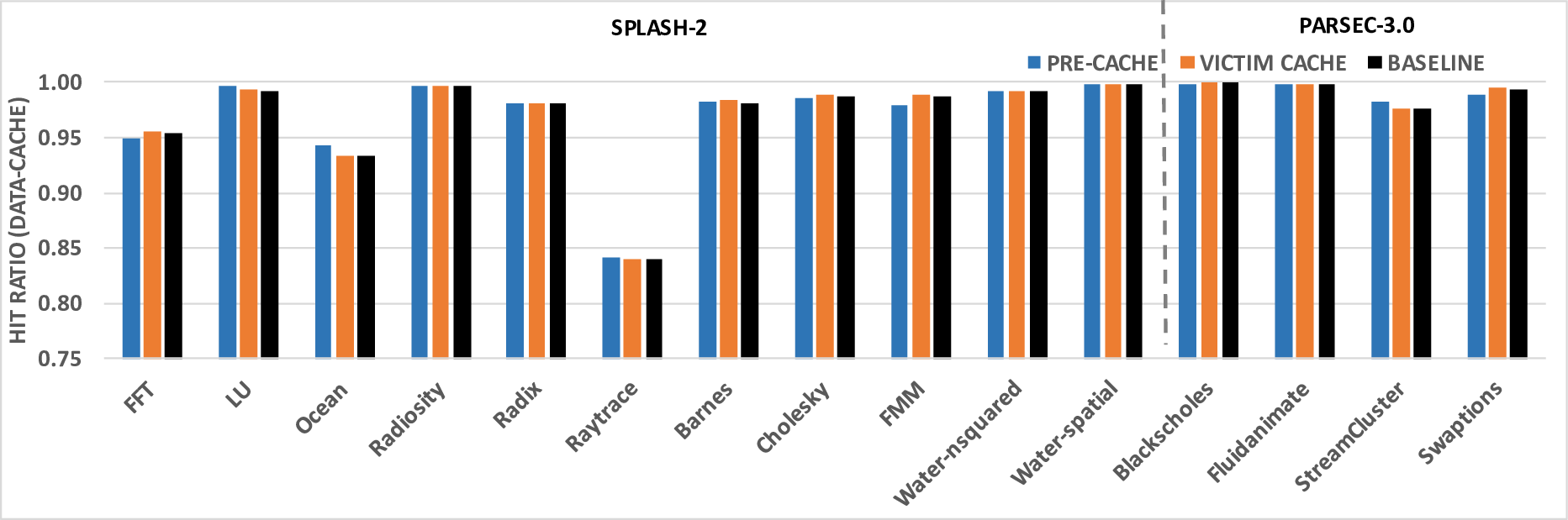

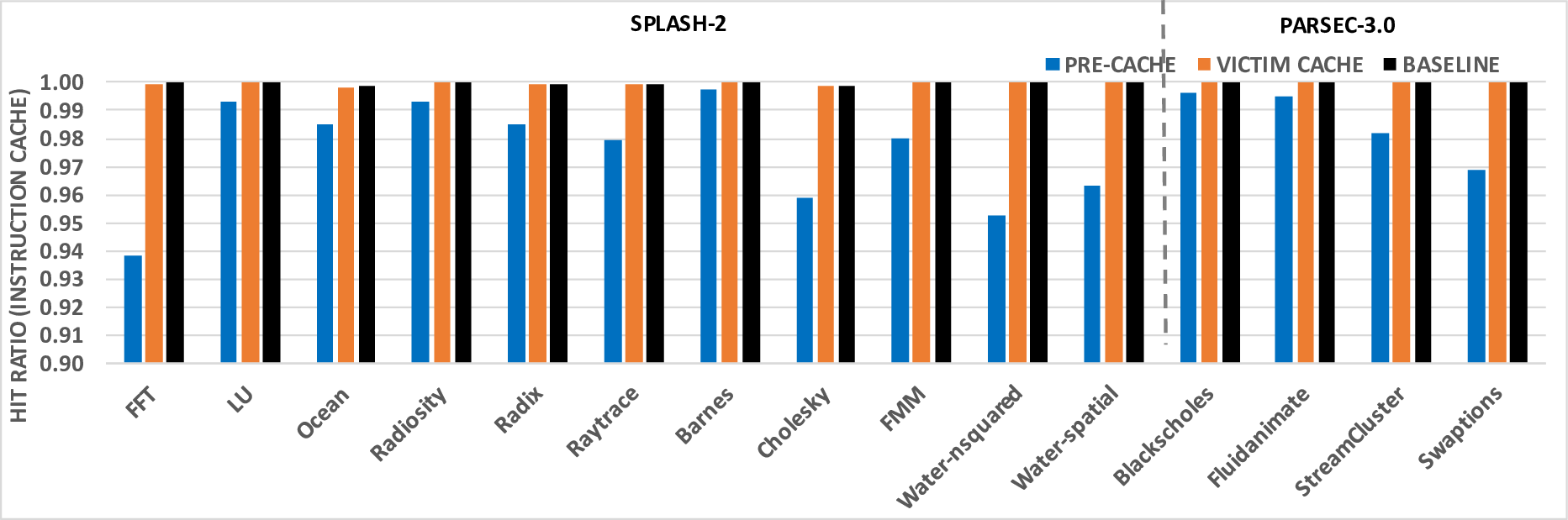

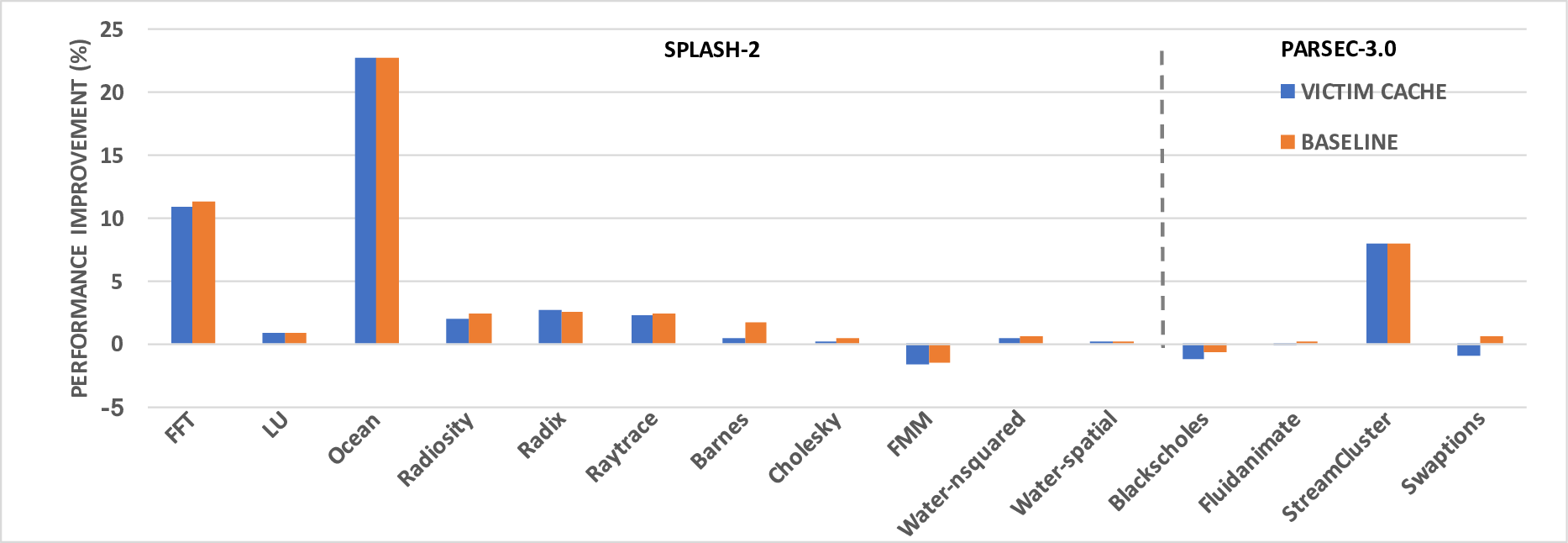

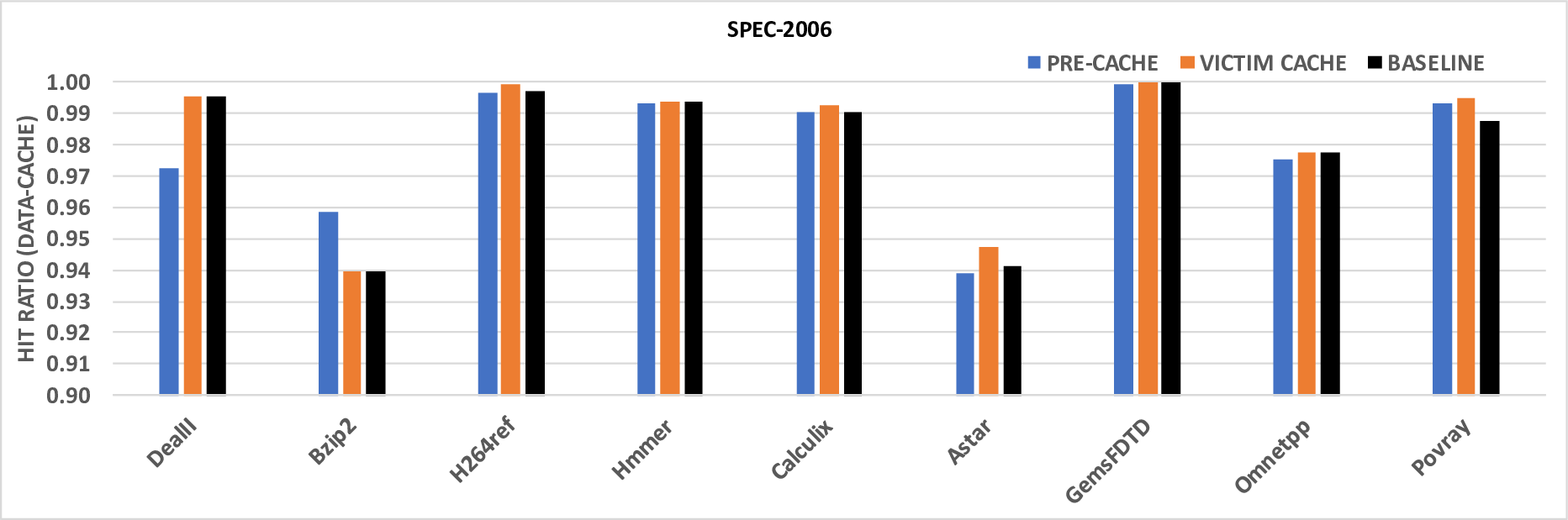

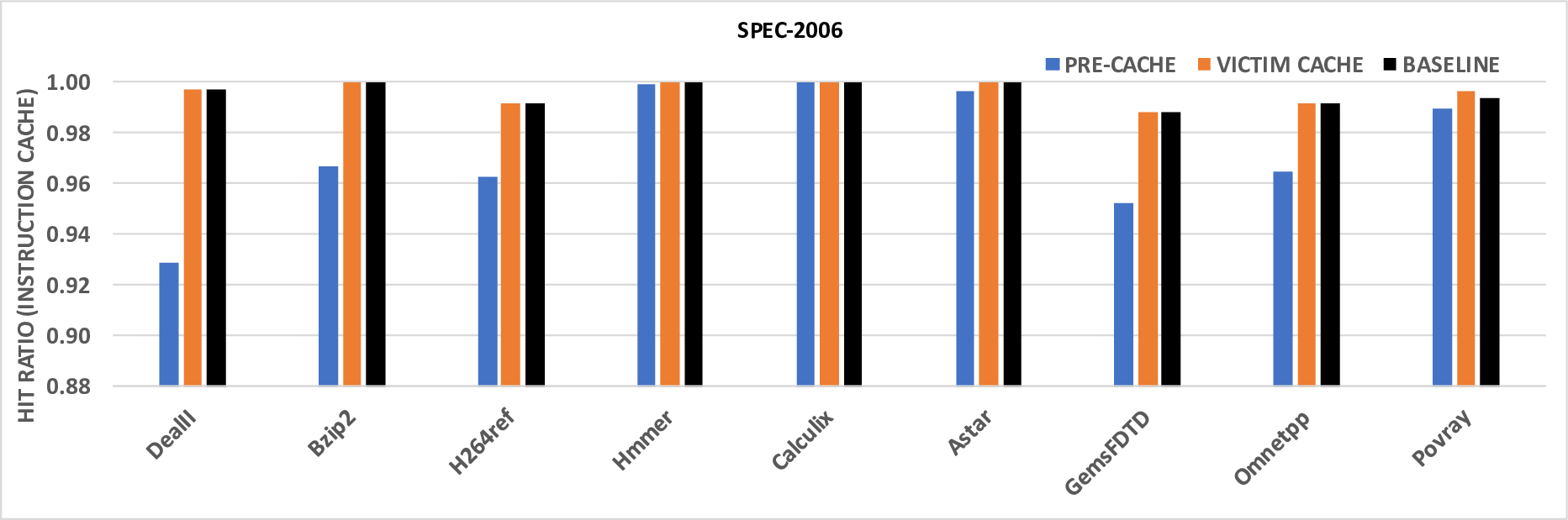

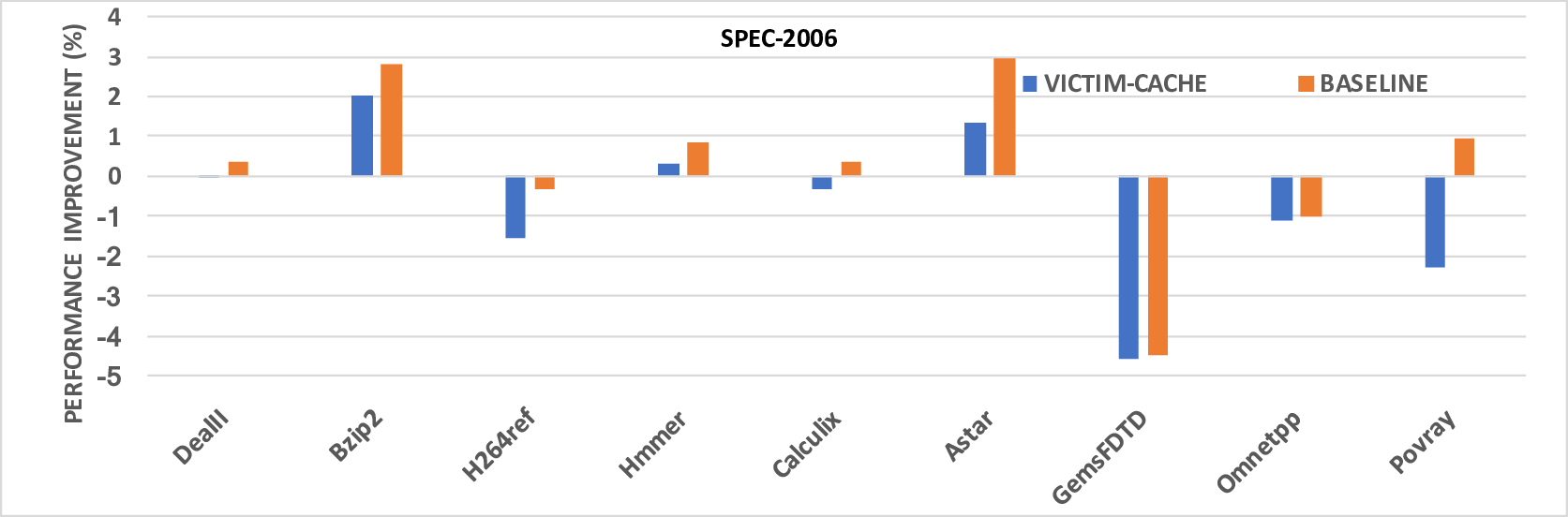

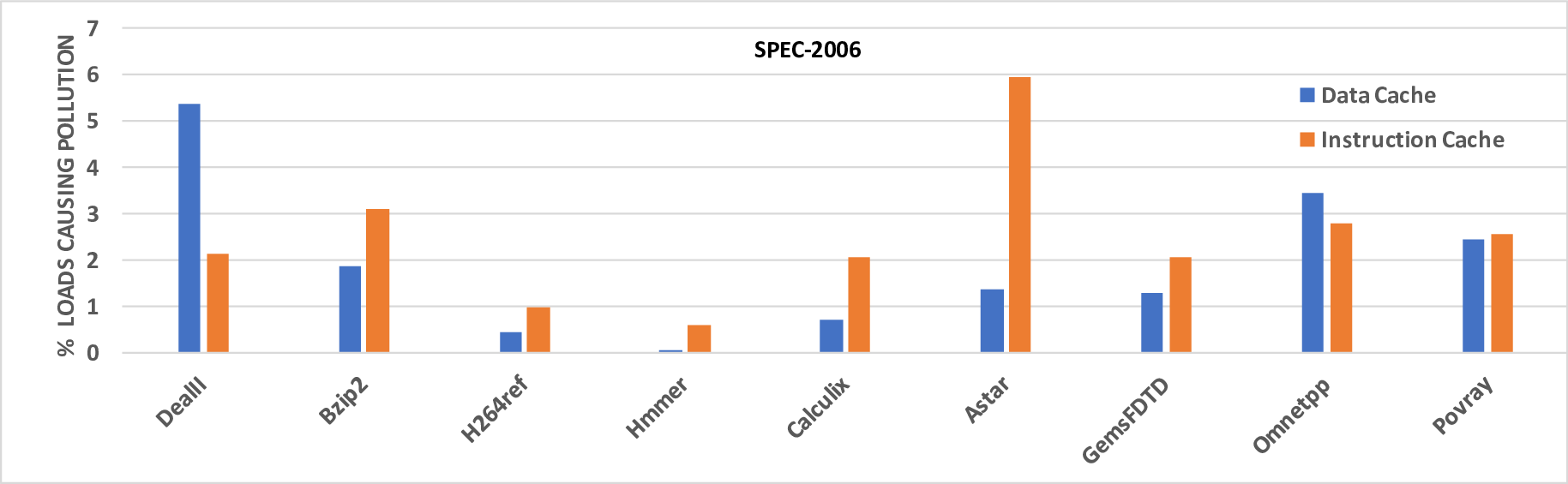

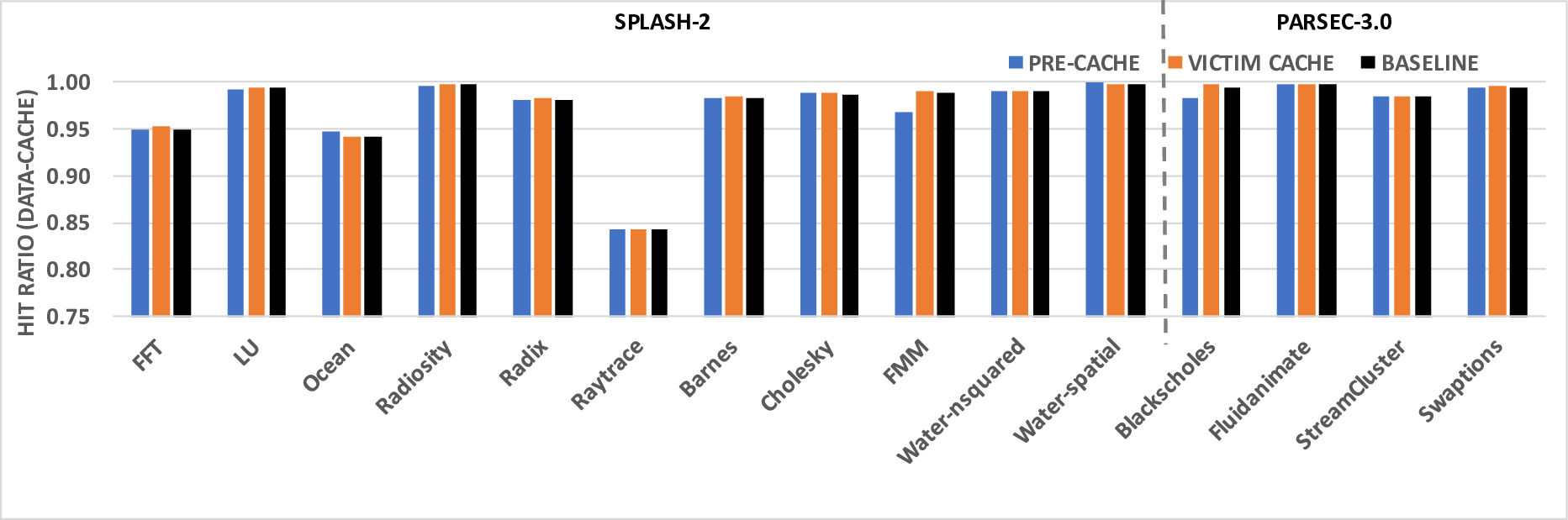

성능 평가에서는 SPEC CPU2006, PARSEC 등 다양한 워크로드에 대해 평균 3~5% 수준의 오버헤드만을 기록하였다. 이는 기존 소프트웨어 기반 완화책에 비해 현저히 낮은 수치이며, 특히 메모리 집약적 애플리케이션에서 거의 영향을 받지 않는다. 따라서 보안과 성능 사이의 트레이드오프를 크게 개선한 솔루션이라고 평가할 수 있다.

요약하면, 이 논문은 추측 실행과 순서 뒤섞기 메커니즘이 남기는 마이크로아키텍처 부작용을 하드웨어 수준에서 근본적으로 차단함으로써 멜트다운·스펙터 및 그 변종을 효과적으로 방어한다. 향후 CPU 설계에 이와 같은 보안‑우선 마이크로아키텍처 기능을 표준화한다면, 사이드 채널 공격에 대한 시스템 전반의 신뢰성을 크게 향상시킬 수 있을 것이다.

📄 논문 본문 발췌 (Excerpt)

📸 추가 이미지 갤러리