Bit-Vector Abstractions to Formally Verify Quantum Error Detection & Entanglement

As the number of qubits increases, quantum circuits become more complex and their state space grows rapidly. This makes functional verification challenging for conventional techniques. Ensuring correctness is especially critical for quantum error cor…

Authors: Arun Govindankutty

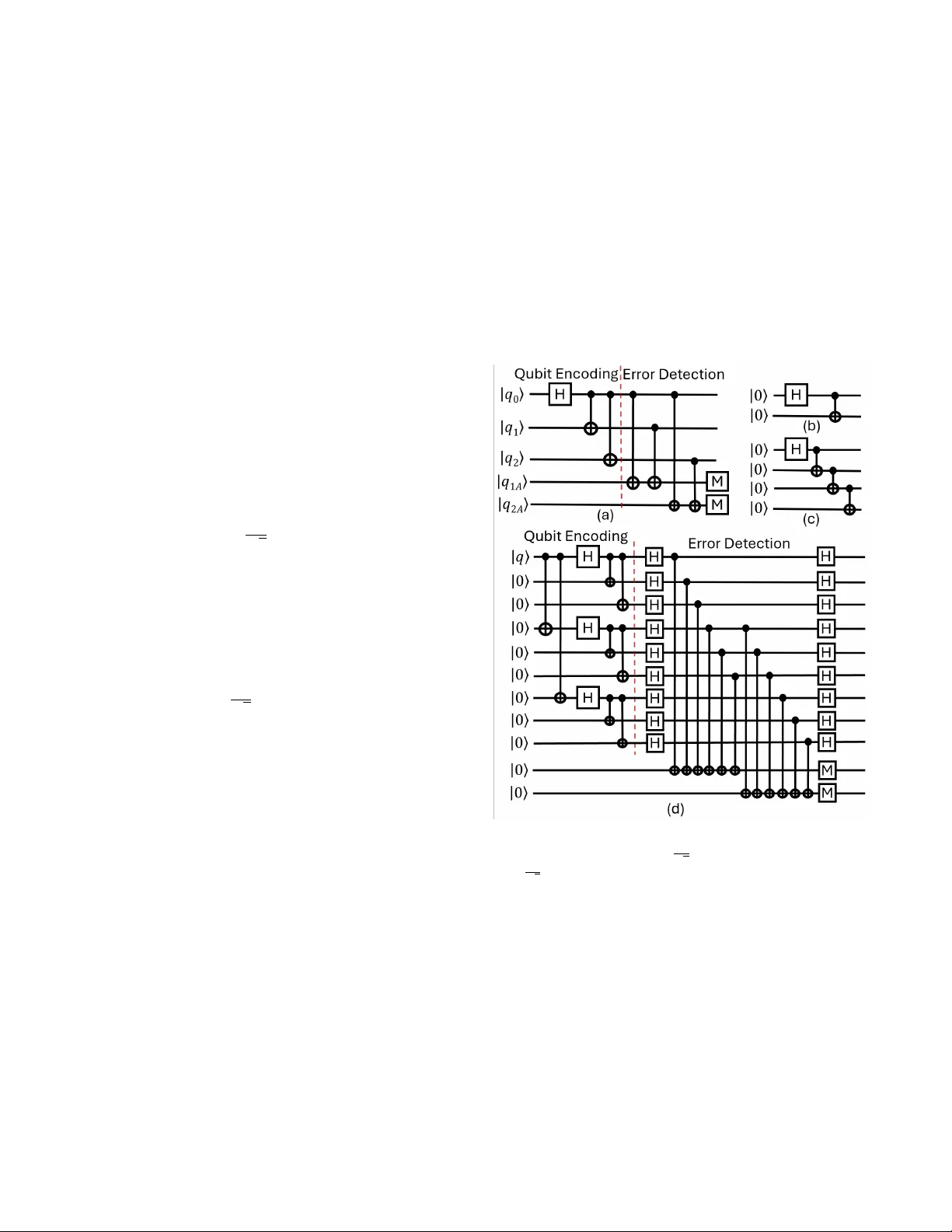

Bit-V ector Abstractions to F ormally V erify Quantum Error Detection & Entanglement Arun Govindankutty Electrical & Computer Engineering, North Dakota State Univer sity , F ar go, ND USA ©2026 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collectiv e works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. Abstract —As the number of qubits increases, quantum circuits become more complex and their state space gr ows rapidly . This makes functional verification challenging for conv entional techniques. Ensuring correctness is especially critical for quan- tum error correction and entanglement generation. This paper presents a novel application of bit-vector based abstraction methodology for formal verification of quantum circuits where superposition and functional behaviour can be decoupled. The approach is applied to error detection circuits f or 2-qubit, 3- qubit, and Shor 9-qubit quantum codes, as well as Bell-state and GHZ-state generation circuits. The error detection circuits and the Bell-state generation circuit are verified in less than a second and 25MB memory . GHZ circuits with up to 8,192 qubits are verified in under three minutes using a maximum of 23.2,GB of memory . The results demonstrate the versatility , scalability , and effectiveness of the proposed appr oach. Index T erms —Bell state, Entanglement, Formal V erification, GHZ state, Quantum Circuits, Quantum Computing, Quantum Error Codes I . I N T RO D U C T I O N Quantum computing has the potential to outperform clas- sical computing in sev eral application domains. These in- clude communication, machine learning, material science, medicine, and optimization, and collectiv ely motiv ate the pursuit of quantum advantage [1]–[5]. Quantum algorithms exploit uniquely quantum phenomena, such as superposition and entanglement, to solve problems that are intractable for classical computers. Entanglement of qubits plays a central role in the realization of multi-qubit quantum systems and the effecti ve execution of quantum algorithms. Also, current quantum hardware is highly susceptible to errors [6]–[9]. This vulnerability limits the reliability of quantum computations. Therefore, verifying circuits that generate entanglement and provide error resilience is essential for the practical advance- ment of quantum computing. V erifying quantum circuits is challenging due to sev eral inherent factors. Qubit superposition, state collapse during measurement, and the exponential growth of the Hilbert space significantly increase verification complexity . As a result, tra- ditional verification techniques become inef ficient for quantum circuits. F ormal methods can address these challenges by using abstractions to enable reliable, robust, and ef ficient verification of quantum systems [10]–[12]. This work proposes a formal methodology for the functional verification of quantum circuits. The method is applied to error detection circuits of v arious quantum error correction codes, Bell-state generation, and Greenberger-Horne-Zeilinger (GHZ) state preparation. The key contributions of this work are summarized as follows: • A bit-vector abstraction that reduces quantum error de- tection, Bell-state generation, and GHZ-state preparation circuits from the Hilbert space representation to a bit- vector domain. • Functional abstractions of quantum gates tailored for quantum error detection, Bell-state generation, and GHZ- state preparation circuits. • Formal specification and verification of correctness prop- erties for quantum error detection, Bell-state generation, and GHZ-state preparation circuits. The proposed approach provides a scalable and rigorous framew ork for the formal verification of quantum circuits. I I . T H E O R E T I C A L B AC K G RO U N D This section pro vides a brief background on qubits, quantum gates and circuits, quantum errors, and syndrome extrac- tion. For a more comprehensiv e understanding of quantum computing fundamentals, readers may refer to [13], [14]. In classical computing, information is processed using bits , which take values of 0 or 1. In quantum computing, howe ver , information is represented using qubits (short for quantum bits). Mathematically , a qubit is expressed as a vector in Dirac notation: | ψ ⟩ = α | 0 ⟩ + β | 1 ⟩ , where | ψ ⟩ represents the quantum state of the qubit. | 0 ⟩ and | 1 ⟩ denote the computational basis vectors. The coef ficients α, β ∈ C , | α | 2 and | β | 2 are the probability amplitudes, constrained by the normalization condition α 2 + β 2 = 1 . Since the computational basis vectors are orthonormal, a qubit state is a linear superposition of these basis states. The individual computational basis vectors are defined as follows: | 0 ⟩ = 1 0 , and | 1 ⟩ = 0 1 (1) In quantum computing, computation is carried out by evolv- ing the quantum states of qubits ov er time. This ev olution is governed by unitary operators, commonly referred to as quantum gates. A quantum circuit consists of an ordered sequence of such gates. It specifies the step-by-step operations used to solve a given problem. Accordingly , a quantum circuit can be viewed as a quantum program or a quantum algorithm, as it encodes the logical structure of the computation [15]. A multi-qubit system with n qubits is represented by a state vector in a 2 n -dimensional Hilbert space. The quantum state is expressed as | Ψ ⟩ = X x ∈{ 0 , 1 } n α x | x ⟩ . (2) The exponential gro wth of this state space is a key source of quantum computational power . It also makes verification of quantum circuits complex. Measurement projects the quantum state onto a basis state. For a measurement in the computational basis, the probability of observing an outcome x is giv en by Pr( x ) = | α x | 2 . (3) This inherent probabilistic behaviour makes reasoning about correctness challenging. It moti vates the use of formal methods that can reason ov er distributions of measurement outcomes. A. Quantum Entanglement Entanglement is a uniquely quantum correlation between subsystems. A multi-qubit state is entangled if it cannot be expressed as a tensor product of individual qubit states. For example, the Bell-state | Φ + ⟩ = 1 √ 2 ( | 00 ⟩ + | 11 ⟩ ) (4) exhibits maximal entanglement. Figure 1 (b) elucidates the quantum circuit for this Bell state generation. The GHZ state is an entangled quantum state in volving three or more qubits [16]. The generalized GHZ state consists of m > 2 subsystems. For a system of m qubits (qubits imply two-dimensional system), the GHZ state is gi ven by | GHZ ⟩ = 1 √ 2 | 0 ⟩ ⊗ m + | 1 ⟩ ⊗ m , (5) where | 0 ⟩ ⊗ m and | 1 ⟩ ⊗ m denote the basis states | 00 . . . 0 ⟩ and | 11 . . . 1 ⟩ , respectively . Figure 1(c) shows the GHZ-state generation for 4-qubit system. Entanglement is a key resource for many quantum al- gorithms. It violates classical assumptions of locality and independence. As a result, classical verification techniques are inadequate, which motiv ates the development of quantum- specific formal reasoning framew orks. B. Quantum Error s and Err or Correcting Codes Errors in an algorithm or a program occur when the out- put deviates from the expected result for a given input. In quantum circuits, these errors originate from complex physical interactions gov erning the system [17], [18]. They can arise due to coherent quantum errors caused by incorrect gate appli- cations, en vironmental decoherence, qubit loss, state leakage, measurement inaccuracies, and initialization errors. T o detect and mitigate these errors, qubit encoding techniques hav e been de veloped, enabling reliable quantum error detection and correction. Among the most widely studied error detection codes are the 2-qubit codes [19], 3-qubit codes [20], and the Shor 9-qubit code [21]. In all qubit encoding schemes, the logical qubit | ψ ⟩ L is represented using multiple physical qubits. For instance, in the 2-qubit code, the logical qubit is expressed as | ψ ⟩ L = | 0 ⟩ L + | 1 ⟩ L , where | 0 ⟩ L 7→ | 00 ⟩ , and | 1 ⟩ L 7→ | 11 ⟩ . Similarly , in the 3-qubit code, the logical basis states are defined as | 0 ⟩ L 7→ | 000 ⟩ , and | 1 ⟩ L 7→ | 111 ⟩ . The 9- qubit code extends this concept by encoding each logical qubit using three repetitions of the 3-qubit code, with entanglement introduced through controlled-NO T (C-NOT) gates to enhance error detection and correction capabilities. In general, 2-qubit, 3-qubit, and 9-qubit codes can correct a single qubit flip err or . Additionally , the 9-qubit code has the capability to correct a single phase flip err or occurring in any one of the 3-qubit logical blocks. Fig. 1. Figure sho ws quantum circuits for the follo wing: (a) 3-qubit code with error detection. (b) Bell state ( 1 √ 2 ( | 0 ⟩ + | 1 ⟩ ) ). (c) GHZ-state with 4- qubits ( 1 √ 2 ( | 0000 ⟩ + | 1111 ⟩ ) ). (d) 9-qubit Shor code with error detection. H indicates Hadamard gate and M indicates measurement operation on qubits. The error detection circuits are designed to detect errors in a quantum system while preserving the original qubit states. Figure 1(a) shows the 3-qubit error detection code along with the error detection circuit. In this circuit, qubits q 0 , q 1 , q 2 form the logical qubit | ψ ⟩ L , while qubits q 1 A and q 2 A serve as ancilla qubits, | ψ ⟩ A . For simplicity , we com- bine both the ancilla and the logical qubits into a single representation. The combined representation is as follo ws: | ψ ⟩ A | ψ ⟩ L = | 00 ⟩| 000 ⟩ = | 00000 ⟩ . For the 3-qubit code, when no errors occur , the ancilla qubits should hold the state ‘00’. Howe ver , in the presence of a qubit-flip error, the ancilla qubits can take values ‘01’, ‘10’, or ‘11’, as summarized in T able I. An error detection T ABLE I E R RO R C O DE T AB L E F O R 3 - Q U BI T C OD E Ancilla V alue ( q 2 A q 1 A ) Qubit State Inference 00 | 000 ⟩ + | 111 ⟩ No Error 11 | 001 ⟩ + | 110 ⟩ 1 st qubit flip 01 | 010 ⟩ + | 101 ⟩ 2 nd qubit flip 10 | 100 ⟩ + | 011 ⟩ 3 rd qubit flip circuit consists of Hadamard (H) gates and C-NO T gates. The matrix representation of the gates are gi ven belo w . H = 1 √ 2 1 1 1 e π i = 1 √ 2 1 1 1 − 1 (6) C-NO T = 1 0 0 0 0 1 0 0 0 0 0 1 0 0 1 0 (7) Figure 1 (d) shows the Shor-9-qubit code along with the quantum circuit for detecting phase flip errors. The ancilla qubit values ‘00, 11, 01 and 10’ correspond to no-error , phase flip in the first, second and third logic blocks respectively . By projecting the error information onto the ancilla qubits, the circuit ensures that the quantum state of the data qubits remains intact, enabling reliable error detection and correction. C. F ormal V erification Formal verification is a rigorous v alidation framework based on mathematical reasoning and proofs. It systematically analyses the entire design space in contrast to traditional testing which analyses specific test scenarios. This enables the detection of corner-case bugs that may be missed by con ventional methods. As a result, formal verification provides strong guarantees of correctness. Formal methods are widely used in software verification, hardware verification, and VLSI design, where reliability and accuracy are critical [22]–[24]. Recent research has focused on extending these techniques to quantum circuit verification [11], [25]. In this work, we propose a formal method to verify quantum circuits for error detection and entanglement generation. I I I . E X I S T I N G A P P RO AC H E S This section provides a concise revie w of existing formal methods for quantum algorithm verification and highlights the unique contributions of our proposed approach. While current verification techniques focus on v alidating various quantum al- gorithms, they do not specifically address the critical challenge of error detection circuit and entanglement verification. T o the best of our knowledge, this work is the first to tackle this essential requirement, making it highly relev ant in the NISQ (Noisy Intermediate-Scale Quantum) era. By filling this gap, our approach ensures more reliable and scalable verification of quantum error detection mechanisms. Amy [26] proposes a verification methodology based on dyadic arithmetic and re write rules using the Haskell theorem prov er . In this approach as qubit count increases, integer ov erflow issues arise, leading to verification failures. The largest quantum circuit verified using this method contains 96 qubits, whereas our proposed approach is capable of verifying circuits with up to 8,192 qubits demonstrating significantly greater scalability . Similarly , Seiter et al. [27] present a property-checking method utilizing multiple-valued decision diagrams. While they successfully verify Grover’ s search algorithm, their ap- proach is limited to circuits with a maximum of 10 qubits, highlighting significant scalability constraints. Burgholzer and W ille [28], as well as Y amashita and Markov [29], propose equiv alence checking as a method for quantum circuit verification. Their approach relies on the av ailability of an already verified reference circuit to perform the v erification process. Also, when a circuit cannot be reduced to binary space, their method resorts to a hybrid approach that incorporates Hilbert space representations, which significantly limits scalability . As a result, their technique can v erify circuits with a maximum of 128 qubits, posing challenges for larger - scale quantum systems. Our approach does not require a verified reference circuit and reduces the entire problem to bit-vector space providing scalability upto 8,192 qubits. Govindankutty et al. [30]–[32] introduced symbolic ab- stractions to reduce quantum circuits to a bit-vector repre- sentation. Their approach was applied to the verification of Quantum Fourier T ransform, its in verse circuits, and quan- tum data encoding circuits only . They do not address error detection or entanglement generation. In this work, we build on these abstractions and extend their scope. The proposed framew ork supports the verification of a broader class of quantum circuits, including quantum error detection codes and quantum entanglement generation circuits. Through this work, we demonstrate the versatility of symbolic abstractions and formal methods for scalable quantum circuit verification. I V . V E R I FI C A T I O N F R A M E W O R K This section presents the abstraction definitions and prop- erties introduced in this work. As discussed in Section II, a qubit is expressed as a linear combination of computational basis states. Therefore, if a circuit is verified to be correct for all basis states, its correctness extends to the entire state space spanned by those states. This observation forms the foundation of the proposed abstraction framew ork. A. Abstractions Definition 1 (Abstract Qubit). An abstract qubit Q is a bit-vector tuple ( s, q ) , wher e s is a 3-bit vector that encodes the superposition status of the qubit, and q is a 2-bit vector that encodes the measur ement status and the computational basis vector value. In this abstraction, s ∈ { b ′ 000 , b ′ 001 , . . . , b ′ 111 } captures the superposition characteristics of the qubit. The value of q represents the computational basis state and whether qubit is measured. When q ∈ { b ′ 00 , b ′ 01 } , the qubit is unmeasured. When q ∈ { b ′ 10 , b ′ 11 } , the qubit has been measured. The most significant bit of q indicates the measurement status, and the least significant bit stores the measured basis value. The prefix b ′ denotes a bit-vector (binary) encoding. Definition 2 (Abstract H Gate). The abstract Hadamar d gate H is a state tr ansition function on an abstract qubit Q ( s, q ) : H ( Q ) = ( ( s + 2 b ′ 001 , q ) if ∀ s ∈ { b ′ 000 , . . . , b ′ 110 } ( b ′ 110 , q ) if s = b ′ 111 (8) In this abstraction frame work, ev en v alues of s indicate that the qubit is not in superposition (i.e., zero or an e ven number of H -gates applied). Odd values of s indicate the qubit is in superposition due to a single or odd number of H -gate applications. The s value thus tracks the number of H -gates applied by modulo-2 ( + 2 ) addition of b ′ 001 . V alue b ′ 000 means no H -gates, b ′ 001 means one H -gate, and so on. For more than seven applications, s toggles between b ′ 110 and b ′ 111 as the length of s is 3 bits. In this work, entanglement circuit uses one H -gate and the error detection circuit uses at most two H -gates. Thus 3 bits are suf ficient for s ( s > b ′ 010 is an error). The H -gate does not modify the q component of the abstract qubit. Definition 3 (Abstract X Gate). The abstract X -gate is a transformation on an abstract qubit Q ( s, q ) , negating the input basis bit without affecting superposition bits. X ( Q ( s, q )) = Q ( s, ¬ q ) (9) Here, Q represents the abstract qubit, and ¬ represents logical negation. Definition 4 (Abstract C-NO T Gate). The abstract C- NO T gate is a transformation on a contr ol-tar get qubit pair ( Q c , Q t ) : C ( Q c , Q t ) = ( ( Q c , Q t ) if q c 0 = 0 ( Q c , Q ( s t , ¬ q t 0 )) if q c 0 = 1 (10) Here, Q c and Q t denote the abstract control and target qubits, and ¬ represents logical negation. The operation leav es the control qubit unchanged. The target qubit basis bit q t 0 is in verted only if the control bit q c 0 is 1; otherwise, it remains the same. The measurement indicators ( q c 1 , q t 1 ) and the su- perposition indicators ( s c , s t ) are unchanged. This abstraction captures the conditional behaviour of the C-NOT gate while preserving the qubit’ s abstract state. Definition 5 (Singular Function). If m = { m 0 , m 1 , . . . , m n − 1 } be a bit vector of length n , wher e m i ∈ { b ′ 0 , b ′ 1 }∀ i ∈ [0 , n ) , then, Singular Function S is defined as: S ( m ) = ( b ′ 1 if P n − 1 i =0 m i = b ′ 1 b ′ 0 otherwise (11) The function S ( m ) returns b ′ 1 if exactly one bit in the vector is set to b ′ 1 . Otherwise, it outputs b ′ 0 . This function is essential for verifying the correctness of error detection circuits. B. Properties W e define the correctness properties next. Separate prop- erties are defined for bit-flip error , phase-flip error detection, and entanglement generation verification. Abstraction aligned properties are defined next. Property 1 (Bit-flip Correctness). ∀ ( s in A i = b ′ 000) ∧ ( s in L i = b ′ 000) , the following conditions must hold: 1) ( s out A i = b ′ 000) ∧ ( s out L i = b ′ 000) , 2) ( q in A i = b ′ 00) ∧ ( q out-1 A i = b ′ 0 D ) , 3) ( q out A 0 = b ′ 11 ⇔ q L 00 = q L 10 ) ∧ ( q out A 1 = b ′ 11 ⇔ q L 00 = q L 20 ) . This property enforces three ke y conditions: First, both an- cilla and logical qubits must preserve their superposition states throughout the error detection process. No unintended change to the superposition should occur . Second, ancilla qubits must be properly initialized, and should not be measured until the final output. The symbol D indicates dont-care that is the basis state may be either 0 or 1. Third, ancilla qubits are measured only at the output and acti vated only in the presence of a single bit-flip error . This ensures that each error detection circuit functions correctly , guaranteeing the circuit’ s reliability against ‘bit-flip’ errors. Property 2 (Phase-flip Correctness). ∀ ( s in A i = b ′ 000) ∧ ( s in L i = b ′ 000) , the following conditions must hold: 1) ( s out A i = b ′ 000) ∧ ( s 1 L i = b ′ 001) ∧ ( s out L i = b ′ 010) , 2) ( q in A i = b ′ 00) ∧ ( q out-1 A i = b ′ 0 D ) , 3) S ( q L 0 , q L 1 , . . . , q L 8 ) = ⇒ ⟨ q out A 1 q out A 0 ⟩ = b ′ 1011 if S ( q L 0 , q L 1 , q L 2 ) = 1 , b ′ 1111 if S ( q L 3 , q L 4 , q L 5 ) = 1 , b ′ 1110 if S ( q L 6 , q L 7 , q L 8 ) = 1 . This property enforces three key conditions: First, superpo- sition correctness must be maintained. Ancilla qubits preserve their superposition states, while logical qubits contain exactly one Hadamard ( H ) gate at the beginning and one at the end. This ensures that the s component of each logical qubit remains at b ′ 001 during extraction. Second, ancilla qubits must be properly initialized and remain unmeasured until the final output stage. The symbol D indicates dont care, that is, the qubit’ s basis state may be 0 or 1. Third, ancilla qubits reflect single-qubit phase-flip errors in the logical qubits. If exactly one of q L 0 , q L 1 , . . . , q L 8 is flipped, the ancilla qubits q A 1 and q A 0 indicate the affected logical block. For example, b ′ 1010 indicates no error, while errors in the first, second, or third 3-qubit blocks correspond to b ′ 1011 , b ′ 1111 , and b ′ 1110 , respectiv ely . This mapping enables precise phase-flip error detection within the Shor 9-qubit code. Property (Entanglement Correctness). F or a quantum system Q = { Q 1 , Q 2 , . . . , Q m } to be entangled, the following conditions must hold: 1) ( s in 1 = b ′ 000) ∧ ( s 1 1 = b ′ 001) ∧ ( s out 1 = b ′ 001) , 2) ( s in 2 = s in 3 = · · · = s in m = b ′ 000) ∧ ( s out 2 = s out 3 = · · · = s out m = b ′ 000) , 3) ∀ i, j ∈ { 1 , 2 , . . . , m } , ( if , i = 1 ∧ q in i = b ′ 00) ∨ ( if i = 1 , ∧ q in 1 = b ′ 01 ∧ q in i = b ′ 00) then , ( q out i = q out j ). This property enforces three requirements. First, the initial qubit Q 1 must enter superposition through a single Hadamard ( H ) gate applied as the first operation. Its superposition state is b ′ 000 at input and remains b ′ 001 after the first stage and throughout the circuit. Second, the remaining qubits Q 2 , . . . , Q m must nev er enter superposition. No H -gate is applied to these qubits, and their superposition state remains s = b ′ 000 . Third, all qubits must share the same output basis state when the first qubit is initialized to either | 0 ⟩ or | 1 ⟩ and all remaining qubits are initialized to | 0 ⟩ (i.e., q in 1 ∈ { b ′ 00 , b ′ 01 } and q in i = b ′ 00 for all i = 1 ). The output must satisfy q out 1 = q out 2 = · · · = q out m , which represents the states | 00 . . . 0 ⟩ or | 11 . . . 1 ⟩ . Note that this condition accurately captures the requirement of equal superposition of the basis states for the first qubit by application of H -gate required for entanglement generation as well. V . V E R I FI C A T I O N M E T H O D O L O G Y The quantum circuit under test is abstracted from Hilbert space to bit-vector space using the abstractions (Section IV -A). The abstract circuit is encoded in SMT (Satisfiability Modulo Theory) and verified for functional correctness. Errors are injected into the abstract circuit to ev aluate the proposed methodology . The correctness of the approach is formally es- tablished through the lemmas presented below . These lemmas show that the method can detect errors in quantum circuits for both error detection and entanglement generation. Lemma 1. If any ancilla qubit is initialized incorrectly or subjected to a H -gate, then Property 1 (bit-flip correctness) and Property 2 (phase-flip correctness) are violated. Lemma 2. If a Hadamard gate is missing from or incorrectly applied to any logical qubit, then Property 1 (bit-flip correct- ness) and Property 2 (phase-flip correctness) are violated. Lemma 3. For bit-flip error detection, any misconfiguration of CNO T gates in the circuit, including incorrect control or target qubits, missing, or extra CNO T gates, result in a violation of Property 1. Lemma 4. For phase-flip error detection, any misconfigura- tion of CNO T gates in the circuit, including incorrect control or target qubits, missing, or extra CNO T gates, result in a violation of Property 2. Lemma 5. Any misconfiguration in Bell-state or GHZ-state generation circuits violates Property 3. This includes missing or extra H gates, missing or extra C-NO T gates, and incorrect control or target qubits in C-NO T gates that result in a non- entangled state. Lemma 6. Any combination of the above lemmas violates at least one of the properties 1–3, flagging every error in functional verification. Theorem 1. An err or in the err or detection cir cuit results in the violation of one or both of Pr operties 1 and 2 dur- ing verification of the abstracted circuit, indicating incorr ect functionality . Theorem 2. An err or in the entanglement gener ation circuit r esults in the violation of pr operty 3 during the verification of the abstracted circuit, indicating incorrect functionality . Proofs for the above lemmas and theorems are straightfor- ward and omitted for bre vity . V I . E X P E R I M E N T A L R E S U LT S Experiments for generating the benchmarks, including the abstractions, circuits, and properties are encoded in the SMT - LIB language. The properties were verified using the Z3 Theorem Prover (version 4.14.1) [33]. All experiments were conducted on an Intel®Core™Ultra 9 285K CPU running at 3.2 GHz, 192 GB of RAM, and RHEL 9 (64-bit), running the RHEL-9.5 64-bit operating system. T able II summarizes the T ABLE II V E RI FI C A T I O N R E S ULT S F O R E R RO R D E T EC T I O N Quantum Code T ime(s) Memory(MB) 2-qubit bit-flip 0.01 17.7 3-qubit bit-flip 0.01 17.7 9-qubit phase-flip 0.01 25.7 Bell state generation 0.01 17.7 verification results for the error detection and the Bell-state generation circuits. The Quantum Code column identifies the circuit type. Columns T ime and Memory report the ex ecution time the peak memory usage in seconds and megabytes, respectiv ely . All circuits were verified in 0.01s. The memory usage for each verification run remained below 25MB. T ABLE III V E RI FI C A T I O N R E S ULT S F O R E N T A N GL E M E NT G E NE R A T I O N Qubit Count No-Error Error Time (s) Memory (MB) Time (s) Memory (MB) 4 0.01 17.4 0.01 17.7 8 0.01 17.4 0.01 17.7 16 0.01 17.5 0.01 17.8 32 0.01 17.7 0.01 18.0 64 0.01 18.6 0.01 18.7 128 0.02 23.0 .02 23.0 256 0.05 39.9 0.05 39.9 512 0.24 115 0.25 115 1024 1.25 393 1.28 393 2048 6.71 1,624 6.68 1,624 4096 32.7 6,173 32.0 6,173 8192 138 23,677 139 23,677 GHZ-state (entanglement) circuits were verified with qubit counts ranging from 4 to 8,192 to demonstrate scalability of the proposed methodology . T able III reports the corresponding verification results. The Qubit Count column indicates the number of qubits in the circuit. The T ime and Memory columns report the execution time in seconds and the peak memory usage in megabytes for both the correct and erroneous circuits. The reported error corresponds to a control-qubit error at qubit-2. The e xecution time and memory usage are comparable for correct and erroneous circuits. All other error scenarios were also verified and exhibited similar resource usage. These results are omitted from reporting for brevity . The proposed approach is currently applicable to class of quantum circuits in which superposition can be decoupled from functional behaviour . The results demonstrate the ef ficiency , scalability , and robustness of the proposed approach. V I I . C O N C L U S I O N A N D F U T U R E D I R E C T I O N S This paper presents a bit-vector–based abstraction for for- mally verifying quantum circuits in which superposition can be decoupled from functional behaviour . The framework re- duces quantum circuit verification from the Hilbert space representation to a bit-vector domain using abstract qubit and gate models. Its versatility is demonstrated by verifying error detection circuits for multiple quantum error-correcting codes, as well as Bell-state and GHZ-state generation circuits. Scalability and efficiency are sho wn by lo w veri fication time, modest memory usage, and support for large qubit counts. Future work will focus on extending the proposed abstrac- tion framew ork to support more general classes of quantum circuits, including those inv olving stabilizer codes, as well as broader categories of quantum algorithms. Such extensions are expected to improve the reliability and scalability of verification techniques for fault-tolerant quantum computing. Furthermore, the results demonstrate the potential of SMT solvers for large scale quantum circuit verification and en- courage continued research into automated formal methods for quantum systems. A C K N O W L E D G M E N T The author thanks Dr . Kushal Ponugoti for the engaging dis- cussions while working on the quantum error detection section, and Dr . Benjamin D. Braaten for providing the computational resources used in the experiments. R E F E R E N C E S [1] V . Hassija, V . Chamola, A. Goyal, S. S. Kanhere, and N. Guizani, “Forthcoming applications of quantum computing: peeking into the future, ” IET Quantum Communication , vol. 1, no. 2, pp. 35–41, 2020. [Online]. A vail- able: https://ietresearch.onlinelibrary .wiley .com/doi/abs/10.1049/iet- qtc.2020.0026 [2] G. Arun and V . Mishra, “ A review on quantum computing and communi- cation, ” in 2014 2nd International Conference on Emerging T echnology T rends in Electr onics, Communication and Networking , 2014, pp. 1–5. [3] J. P , S. Hariharan, V . Madhivanan, S. N, M. Krisnamoorthy , and A. K. Cherukuri, “Enhanced qsvm with elitist non-dominated sorting genetic optimisation algorithm for breast cancer diagnosis, ” IET Quantum Communication , vol. n/a, no. n/a. [Online]. A vailable: https://ietresearch.onlinelibrary .wiley .com/doi/abs/10.1049/qtc2.12113 [4] M. Kim, D. V enturelli, and K. Jamieson, “T owards hybrid classical- quantum computation structures in wirelessly-networked systems, ” in Pr oceedings of the 19th ACM W orkshop on Hot T opics in Networks , 2020, pp. 110–116. [5] G. Carrascal, P . Hernamperez, G. Botella, and A. d. Barrio, “Backtest- ing quantum computing algorithms for portfolio optimization, ” IEEE T ransactions on Quantum Engineering , vol. 5, pp. 1–20, 2024. [6] P . Shor, “Fault-tolerant quantum computation, ” in Pr oceedings of 37th Confer ence on F oundations of Computer Science , 1996, pp. 56–65. [7] P . W . Shor, “Scheme for reducing decoherence in quantum computer memory , ” Phys. Rev . A , vol. 52, pp. R2493–R2496, Oct 1995. [Online]. A vailable: https://link.aps.org/doi/10.1103/PhysRe vA.52.R2493 [8] M. Brooks, “Beyond quantum supremacy: the hunt for useful quantum computers, ” Natur e , vol. 574, pp. 19–21, 10 2019. [9] J. Preskill, “Quantum computing in the nisq era and beyond, ” Quantum , vol. 2, p. 79, 8 2018. [10] J. Liu, B. Zhan, S. W ang, S. Y ing, T . Liu, Y . Li, M. Y ing, and N. Zhan, “Formal verification of quantum algorithms using quantum hoare logic, ” in Computer Aided V erification , I. Dillig and S. T asiran, Eds. Cham: Springer International Publishing, 2019, pp. 187–207. [11] C. Chareton, S. Bardin, D. Lee, B. V aliron, R. V ilmart, and Z. Xu, “Formal methods for quantum programs: A survey , ” 2022. [12] A. Govindankutty , “ A review of formal methods in quantum-circuit verification, ” Electr onics , vol. 15, no. 5, 2026. [Online]. A vailable: https://www .mdpi.com/2079-9292/15/5/1125 [13] M. A. Nielsen and I. L. Chuang, Quantum Computation and Quantum Information: 10th Anniversary Edition , 10th ed. USA: Cambridge Univ ersity Press, 2011. [14] C. Bernhardt, Quantum Computing for Everyone . MIT Press, 2020. [15] A. Barenco, C. H. Bennett, R. Cleve, D. P . DiV incenzo, N. Margolus, P . Shor, T . Sleator , J. A. Smolin, and H. W einfurter, “Elementary gates for quantum computation, ” Phys. Rev . A , vol. 52, pp. 3457–3467, Nov 1995. [Online]. A vailable: https://link.aps.org/doi/10.1103/PhysRe vA.52.3457 [16] D. M. Greenberger , M. A. Horne, and A. Zeilinger , “Going beyond bell’ s theorem, ” 2007. [Online]. A vailable: https://arxiv .org/abs/0712.0921 [17] S. J. Devitt, W . J. Munro, and K. Nemoto, “Quantum error correction for beginners, ” Reports on Pr ogr ess in Physics , vol. 76, p. 076001, 7 2013. [18] D. A. Lidar and T . A. Brun, Quantum err or correction . Cambridge univ ersity press, 2013. [19] D. Gottesman, “ An introduction to quantum error correction, ” in Pro- ceedings of Symposia in Applied Mathematics , vol. 58, 2002, pp. 221– 236. [20] J. Roffe, “Quantum error correction: an introductory guide, ” Contempo- rary Physics , vol. 60, no. 3, pp. 226–245, 2019. [21] P . W . Shor , “Fault-tolerant quantum computation, ” in Proceedings of 37th conference on foundations of computer science . IEEE, 1996, pp. 56–65. [22] O. Hasan and S. T ahar, “Formal verification methods, ” in Encyclopedia of Information Science and T echnolo gy , Thir d Edition . IGI global, 2015, pp. 7162–7170. [23] A. Gupta, “Formal hardware verification methods: A survey , ” F ormal Methods in System Design , vol. 1, pp. 151–238, 1992. [24] T . Schubert and M. V . A. K. K. E. Seligman, F ormal V erification . Elsevier , 2015. [25] A.-J. Quist, J. Mei, T . Coopmans, and A. Laarman, “ Advancing quantum computing with formal methods, ” in F ormal Methods , A. Platzer , K. Y . Rozier , M. Pradella, and M. Rossi, Eds. Cham: Springer Nature Switzerland, 2025, pp. 420–446. [26] M. Amy , “T ow ards large-scale functional verification of univ ersal quan- tum circuits, ” Electr onic Proceedings in Theor etical Computer Science , vol. 287, pp. 1–21, 1 2019. [27] J. Seiter, M. Soeken, R. W ille, and R. Drechsler , “Property checking of quantum circuits using quantum multiple-valued decision diagrams, ” in Reversible Computation , R. Gl ¨ uck and T . Y okoyama, Eds. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013, pp. 183–196. [28] L. Burgholzer and R. Wille, “ Advanced equiv alence checking for quantum circuits, ” IEEE T ransactions on Computer-Aided Design of Inte grated Circuits and Systems , vol. 40, pp. 1810–1824, 9 2021. [29] S. Y amashita and I. L. Marko v , “Fast equiv alence-checking for quantum circuits, ” in 2010 IEEE/ACM International Symposium on Nanoscale Ar chitectur es , 2010, pp. 23–28. [30] A. Govindankutty , S. K. Srinivasan, and N. Math- ure, “Rotational abstractions for verification of quantum fourier transform circuits, ” IET Quantum Communication , vol. 4, no. 2, pp. 84–92, 2023. [Online]. A vailable: https://ietresearch.onlinelibrary .wiley .com/doi/abs/10.1049/qtc2.12055 [31] A. Govindankutty and S. Srinivasan K, “Superposition-based abstrac- tions for quantum data encoding verification, ” IET Quantum Communi- cation , 2025. [32] G. Arun, S. Sriniv asan, and Y . Moshood, “V erification of quantum fourier transform and its in verse via rotational and superposition ab- straction, ” in IEEE International Symposium on Circuits and Systems , 2026. [33] L. De Moura and N. Bjørner , “Z3: An efficient smt solver , ” in Pr o- ceedings of the Theory and Practice of Software , 14th International Confer ence on T ools and Algorithms for the Construction and Analysis of Systems , ser . T ACAS’08/ET APS’08. Berlin, Heidelberg: Springer- V erlag, 2008, p. 337–340.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment