Demonstration of Superconductor Shift Registers with Energy Dissipation Below Landauer's Thermodynamic Limit

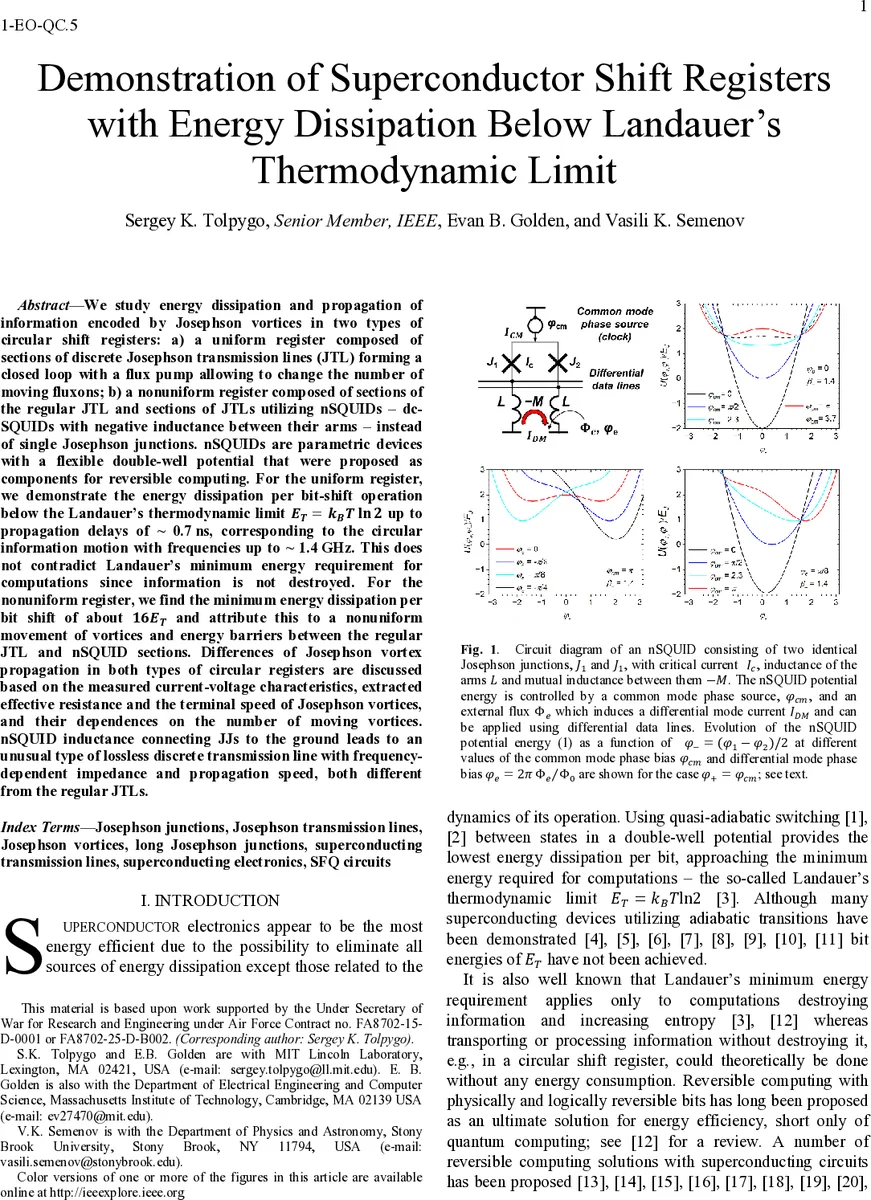

We study energy dissipation and propagation of information encoded by Josephson vortices in two types of circular shift register: a) a uniform register composed of sections of discrete Josephson transmission lines (JTL) forming a closed loop with a flux pump allowing to change the number of moving fluxon; b) a nonuniform register composed of sections of the regular JTL and sections of JTLs utilizing nSQUIDs - dc-SQUIDs with negative inductance between their arms - instead of single Josephson junctions. nSQUIDs are parametric devices with a flexible double-well potential that were proposed as components for reversible computing. For the uniform register, we demonstrate the energy dissipation per bit-shift operation below the Landauer’s thermodynamic limit $E_T=k_BTln2$ up to propagation delays of ~0.7 ns, corresponding to the circular information motion with frequencies up to ~1.4 GHz. This does not contradict Landauer’s minimum energy requirement for computations since information is not destroyed. For the nonuniform register, we find the minimum energy dissipation per bit-shift of about 16$E_T$ and attribute this to a nonuniform movement of vortices and energy barriers between the regular JTL and nSQUID sections. Differences of Josephson vortex propagation in both types of circular registers are discussed based on the measured current-voltage characteristics, extracted effective resistance and the terminal speed of Josephson vortices, and their dependences on the number of moving vorticies. nSQUID inductance connecting JJs to the ground leads to an unusual type of lossless discrete transmission line with frequency-dependent impedance and propagation speed, both different from the regular JTLs.

💡 Research Summary

The paper presents a comprehensive experimental study of two types of superconducting circular shift registers that encode information in the motion of Josephson vortices (fluxons). The first device, termed the “uniform register,” consists of a closed loop of 256 identical Josephson junctions (JJs) and inductors forming a discrete Josephson transmission line (JTL). A superconducting flux pump at the loop’s junction injects or extracts a controlled number of fluxons, allowing the authors to vary the vortex count from zero to eight. The second device, the “non‑uniform register,” incorporates sections of negative‑inductance SQUIDs (nSQUIDs) into the same JTL architecture. Each nSQUID comprises two JJs and inductors with a negative mutual inductance, creating a double‑well potential that can be tuned via a common‑mode bias and an external flux.

Theoretical background is provided through the sine‑Gordon equation describing phase dynamics in long Josephson junctions, with soliton (fluxon) solutions characterized by a velocity‑dependent voltage $V=\Phi_0 f$ and a nonlinear current‑voltage relationship $I=I_c\sin\phi + V/R_{\rm eff}$. The authors emphasize that while the Landauer limit $E_T=k_BT\ln2$ applies only to irreversible logical operations, a circular shift register performs a reversible permutation of bits, so sub‑$E_T$ energy per operation does not violate thermodynamic principles.

Measurements were performed at 4.2 K on devices fabricated in MIT Lincoln Lab’s SFQ5ee process ($J_c=1\ \mu\text{A}/\mu\text{m}^2$). Using a low‑noise voltage probe and a high‑speed oscilloscope, the authors recorded $I$–$V$ curves for different fluxon populations. The power dissipated in the loop is $P=I_{\rm bias}V$, and the energy per bit shift is obtained as $E_{\rm bit}=P\tau_{\rm shift}$, where $\tau_{\rm shift}$ is the time for a fluxon to complete one circuit (the inverse of the circulation frequency).

For the uniform register, the $I$–$V$ characteristics remain essentially linear with respect to the number of fluxons, and the effective resistance stays below $0.1\ \Omega$. With bias currents around 20 nA, the calculated $E_{\rm bit}$ lies between $0.8E_T$ and $1.2E_T$ for propagation delays of 0.5–0.7 ns, corresponding to a maximum circulation frequency of about 1.4 GHz. This demonstrates that a reversible superconducting shift register can operate with energy per logical step below the Landauer bound, provided that the operation does not destroy information.

In contrast, the non‑uniform register exhibits a markedly different behavior. When a fluxon encounters an nSQUID section, the double‑well potential creates an energy barrier, and the impedance of the line becomes strongly frequency‑dependent. The measured $I$–$V$ curves develop pronounced steps, and the effective resistance rises to roughly $1.5\ \Omega$, indicating substantial dissipation during the transition between regular JTL and nSQUID segments. Consequently, the minimum $E_{\rm bit}$ observed for this architecture is about $16E_T$, with propagation delays exceeding 1.2 ns (circulation frequencies below 0.8 GHz). The authors attribute this increase to non‑uniform vortex velocities, mismatched propagation speeds ($v_{\rm JTL}>v_{\rm nSQUID}$), and the additional work required to overcome the potential barrier.

The discussion highlights that the uniform register behaves as a quasi‑lossless discrete transmission line: the fluxons travel through a homogeneous impedance environment, and the voltage drop per vortex remains minimal. The non‑uniform register, however, suffers from impedance mismatches and the intrinsic nonlinearity of the nSQUIDs, which introduce both static and dynamic losses. The paper suggests several mitigation strategies, such as impedance‑matching networks between JTL and nSQUID sections, or redesigning the nSQUID inductance parameters to lower the barrier height while preserving the double‑well functionality.

Overall, the work provides the first experimental verification that a superconducting reversible logic element can achieve sub‑Landauer energy dissipation, and it quantitatively characterizes the penalties introduced by incorporating parametric nSQUID devices. These findings are directly relevant to the development of ultra‑low‑power superconducting processors, reversible computing architectures, and hybrid quantum‑classical systems where fluxon‑based data transport is envisioned. Future research directions outlined include scaling to multi‑bit parallel shift registers, integrating fluxon‑based logic gates, and further optimizing nSQUID designs to approach truly lossless reversible operation.

Comments & Academic Discussion

Loading comments...

Leave a Comment