Mr.TPL: A Method for Multi-Pin Net Router in Triple Patterning Lithography

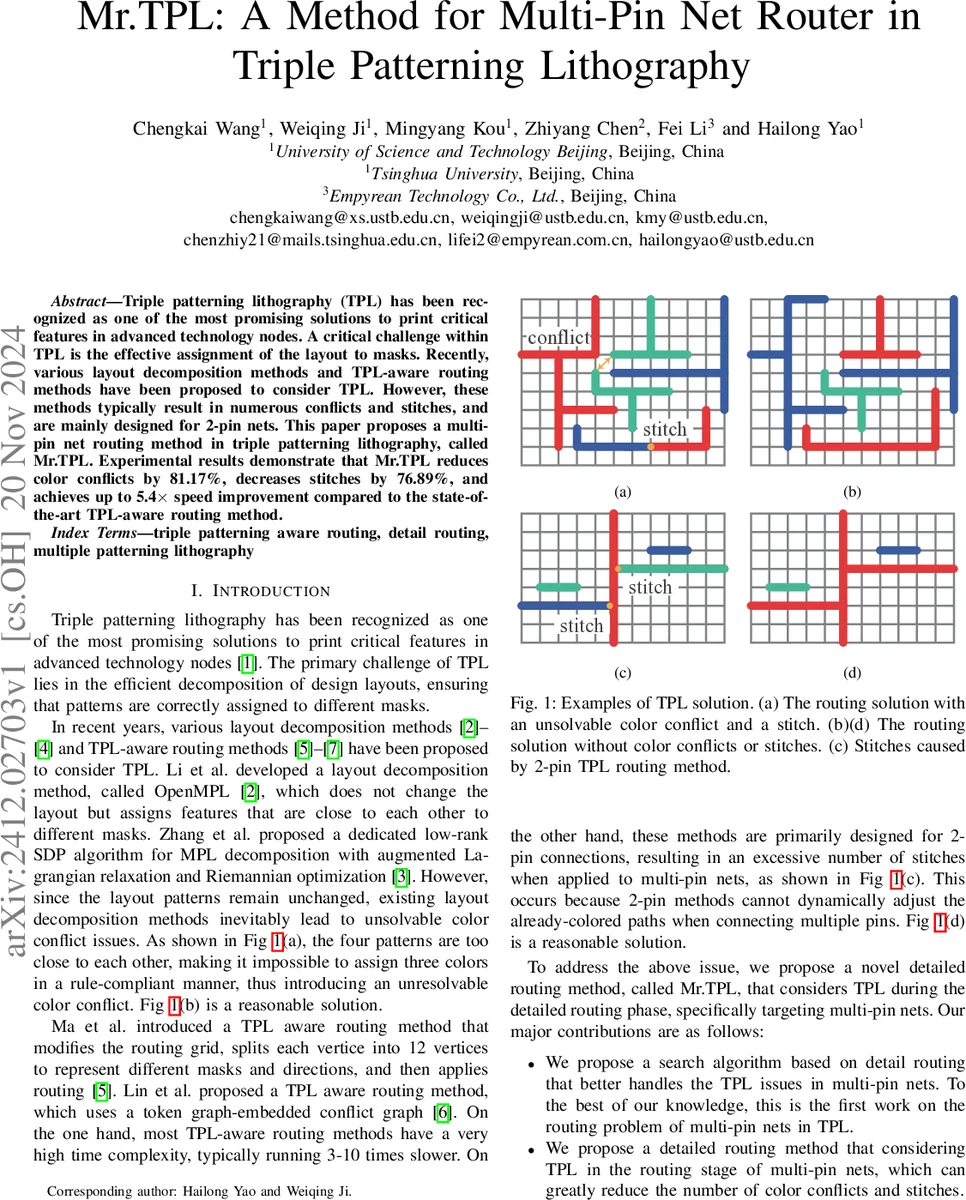

Triple patterning lithography (TPL) has been recognized as one of the most promising solutions to print critical features in advanced technology nodes. A critical challenge within TPL is the effective assignment of the layout to masks. Recently, various layout decomposition methods and TPL-aware routing methods have been proposed to consider TPL. However, these methods typically result in numerous conflicts and stitches, and are mainly designed for 2-pin nets. This paper proposes a multi-pin net routing method in triple patterning lithography, called Mr.TPL. Experimental results demonstrate that Mr.TPL reduces color conflicts by 81.17%, decreases stitches by 76.89%, and achieves up to 5.4X speed improvement compared to the state-of-the-art TPL-aware routing method.

💡 Research Summary

Triple Patterning Lithography (TPL) has become a cornerstone technology for sub‑7 nm semiconductor manufacturing, yet its integration into the physical design flow remains challenging because mask assignment must be considered early to avoid manufacturability issues. Existing layout decomposition and TPL‑aware routing approaches largely focus on 2‑pin nets. When these methods are applied to multi‑pin nets, they generate an excessive number of color conflicts and stitches, leading to lower yield and longer design cycles.

The paper introduces Mr.TPL, a novel detailed routing framework that directly handles multi‑pin nets under TPL constraints. The core innovation is the introduction of a color state represented by a 3‑bit mask (e.g., 111, 101, 110) for each routing segment. This representation allows a segment to keep multiple mask candidates simultaneously during the search phase, postponing the final color decision until back‑tracing.

Mr.TPL builds an undirected graph G = (V, E) from the layout, where vertices correspond to grid intersections and edges to possible wire segments. Each edge carries a color‑state attribute and three cost components: traditional routing cost (length, congestion), stitch cost (penalty for mask changes along a wire), and color‑conflict cost (penalty when adjacent edges share the same mask). The total cost is a weighted sum: Cost(e) = α·Cost_trad(e) + β·Cost_stitch(e) + γ·Cost_color(e). The weights α, β, γ can be tuned to prioritize yield, performance, or area.

Routing proceeds in four stages:

-

Initialization – Load layout, netlist, and global routing guides; construct the routing grid and assign an initial color state of 111 (all masks possible) to vertices covering the first pin of each net.

-

Multi‑pin Search – Using a priority queue (similar to Dijkstra’s algorithm), the algorithm expands from already‑routed vertices toward uncovered pins. For each direction (F, B, R, L, U, D) and each mask (R, G, B), it computes a temporary cost that includes any required stitch penalty if the direction changes the mask relative to the current vertex’s color state. The minimum‑cost mask‑direction pair is selected, the vertex cost is updated, and the vertex is re‑inserted into the queue. This process continues until all pins of the net are connected.

-

Back‑trace and Color Convergence – Once a destination pin is reached, the algorithm back‑traces from the destination to the source, constructing the final routing path. During back‑trace, vertices are grouped into verSets (adjacent vertices sharing the same color state) and segSets (collections of verSets with identical color states). If a stitch is required, the segSet is split; otherwise the whole segment remains in a single color set. The back‑trace gradually collapses each vertex’s color state from a multi‑mask candidate to a single mask, ensuring a conflict‑free final assignment.

-

Rip‑up / Reroute Loop – After routing all nets, a conflict detection step identifies any remaining violations. If conflicts exist and the iteration limit has not been reached, the algorithm performs rip‑up of offending paths, updates history costs to discourage repeated conflicts, and repeats the routing process.

Experimental evaluation uses the ISPD 2015/2016 benchmark suite. Compared with the state‑of‑the‑art TPL‑aware router (reference

Comments & Academic Discussion

Loading comments...

Leave a Comment