Fast-SSC-Flip Decoding of Polar Codes

Polar codes are widely considered as one of the most exciting recent discoveries in channel coding. For short to moderate block lengths, their error-correction performance under list decoding can outperform that of other modern error-correcting codes…

Authors: Pascal Giard, Andreas Burg

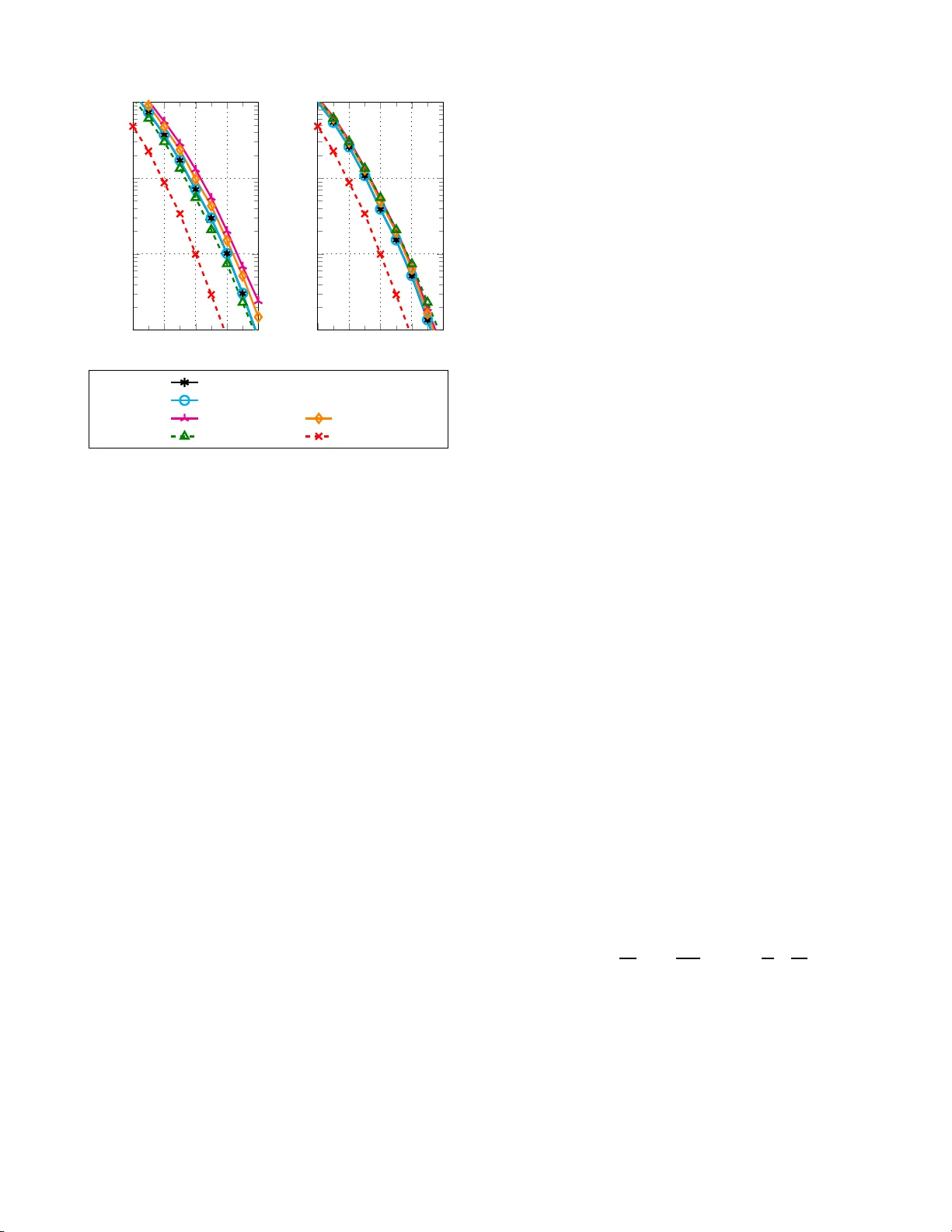

F ast-SSC-Flip Decoding of Polar Co des Pascal Giard and Andreas Bur g T elecommu n ications Circuits Laboratory Ecole polytechniq ue f ´ ed ´ erale de Lausann e (EPFL), 1015 Lausanne VD, Switzerland Email: { pascal.giard,and reas.burg } @epfl.ch Abstract —Polar codes are widely consid ered as one of th e most exciting recent disco veries in channel coding. For short to moderate block lengths, t heir error -correction performance under list d ecoding can outperform that of other mo dern error - correc ting codes. Howeve r , high-speed l ist-based decoders with moderate complexity are challenging to imp lement. Successive- cancellation (SC)-flip decoding was shown to be capable of a competitiv e error -correction performance compared to that of list decoding with a sma ll list size, at a fraction of the c omplexity , but su ff ers from a variable execution time and a higher worst- case latency . In thi s work, we show how to modify the state- of-the-art high-speed SC decoding algorithm to incorporate the SC-flip i d eas. The algorithmic improv ements are presented as well as a verage execution-ti me results tailored to a h ardware implementation. The r esults show that the proposed fast-SSC-flip algorithm has a d ecoding speed close to an order of magnitude better than the previous works while retaining a comparable error -correction perf ormance. I. I ntroduction Polar co des made it into 3GPP’ s next-gen eration mobile- commun ication standard (5G) due to th eir excellent erro r- correction performance under successive-cancellation list (SCL) decoding [1]. Ho wev er , implem enting high-throu g hput SCL decoder s while retainin g a mo d erate complexity is challengin g since the decod er specu lati vely explores multiple candidate solution s in parallel o f which a majo rity is, in the end, aba n doned . As an altern ativ e, Afisiadis et al. propo sed the low-complexity su c cessi ve-cancellation flip ( SCF) deco d ing algorithm [2] which explores candidate solutions sequentially , therefor e a voiding many u nnecessary compu tations. They showed that, for a 1 024-b it polar co d e with a code rate o f 1 / 2 and a 16-bit cyclic red undancy check (CRC ), SCF could match the err o r-correction perf o rmance of SCL decoding with a small list size ( L = 2) if a su ffi cien t numb er of trials were attempted ( T = 32). Howev er, being seque n tial in nature, the instantaneou s d ecoding throughput of SCF deco ding is vari- able and the average throug hput depe nds on the ch annel sign al- to-noise ratio. Nev ertheless, it was shown in [3] th at, under reasonable conditio ns, it had much better average throughpu t and a significan tly lower average d e coding complexity in terms of the area-time p roduct than SC L decodin g. Contributions: In th is paper, we show ho w to merge the SCF decoding a lg orithm with th e state-of-the-art h igh-speed successiv e-cancellation (SC)-based deco ding algo r ithm tha t decomp o ses polar codes into co nstituent codes. W e introduce decision-log -likelihood- r atio (LLR) calculation s, required for SCF decod ing, tailored to the various constituent-co de typ es. W e show that the new decoding algorithm has an error- correction perfor m ance that is e ither virtually the same or v ery close to that of the or ig inal SCF algorithm. Hardware imple- mentation co nsideration s are discussed, and the execution time of the prop o sed algorithm is compa r ed with that of the only SCF-decoder implementation from the literatur e . Outline: The remainder of this p aper starts with Section II which provides backgro und about p olar-code con struction and encodin g , p olar-code representa tio ns and decomposition in constituent codes, an d the decodin g algo rithms on which this work is built. Section III describes th e prop osed new algorithm a nd the decision-LLR equa tions for the various constituent-c o de types. Hardware consider ations are discussed in Section IV, where an a verage ex ecution- time com parison against the state of the art is also p r esented. Finally , Section V conclud e s this paper . II. B a ckgr ound A. Construction and Encoding Polar codes are lin ear block c o des, i.e., the encod ing process implies th e linear transform ation of a vector of bits. This transform ation is structured in a way th at results in a p olar- ization e ff ect, as its len g th tends to infinity , where some of the en coded bits can be d ecoded p erfectly while the others become completely unreliable. In particular, in matrix form, a polar code of length N can be obtained as x = u F ⊗ n , F = " 1 0 1 1 # , (1) where n , log 2 N , u is th e vector of bits to be encod ed, and F ⊗ n is the n th Kronecker p roduct o f F an d F ⊗ 1 = F . T o obtain an ( N , k ) po la r code of rate R = k / N , the k most-reliab le bit locations in u hold the inf ormation bits while the o th er N − k bits, called fro zen b its, are set to a predetermined value (usually 0) . The bit-locatio n reliabilities d epend o n the chann e l type an d co ndition. Many methods have b een pr oposed to calculate these r e liabilities; we use that of T al and V ardy [4]. B. Representations an d Constituen t Codes In addition to the matrix form, polar codes can be repre- sented as a grap h . Fig. 1a sho ws such a representation for an (8 , 5) po lar code, whe re + are mod ulo-2 additions, th e grayed u i ’ s with i ∈ { 0 , 1 , 4 } hold frozen bits, and the black u i ’ s with i ∈ { 2 , 3 , 5 , 6 , 7 } hold the infor mation b its. Encodin g is done by propagating the vector u , in that g raph, from left to right. u 0 + + + x 0 u 1 + + x 1 u 2 + + x 2 u 3 + x 3 u 4 + + x 4 u 5 + x 5 u 6 + x 6 u 7 x 7 (a) Graph v α v β v β l α l α r β r (b) S C Decoder Tree v (c) Fast-SSC Decoder Tree Fig. 1. Gra ph and decoder -tree represent ations of an (8 , 5) polar code. Also from Fig. 1a, notice how polar codes are built re- cursively: th e first h alf ( x 3 0 , [ x 0 , x 1 , x 2 , x 3 ]) of a p olar co de of len gth N = 8 is the result of the element- wise modu lo- 2 addition of two polar cod es of length N v = N / 2 = 4, a n d the o th er half ( x 7 4 ) cor respond s to the second po lar code o f length N v = 4. In other words, any po lar code of len gth N c an be seen as a com position of two sma ller con stituent (polar) codes of leng th N v = N / 2 with k v informa tio n bits. T ak ing into co nsideration th e frozen -bit locations, many of these co nstituent codes can be con sidered as b lo ck code s with a special structure rathe r than as polar codes. As will be b riefly reminded in Sec tio n II- C below , th is structu re can then be exploited to use dedic a ted deco ding a lg orithms which are more e ffi cient than the ge n eric decoding alg orithm for polar code s. Alternatively to the graph representa tio n, it w as shown in [5] that polar codes c a n also be repr esented as bin a ry trees, or decoder trees, wh ere the white and b lack leaf nodes corresp ond to fr o zen-bit an d inform ation-bit locations, respectiv ely . Fig.1 b shows th e decod e r tree rep resentation of th e same (8 , 5 ) p olar code illustrated a s a gr aph in Fig. 1 a. The par t o f the grap h circled by a green dashed line in Fig. 1a correspond s to the node v of width N v circled in the sam e way in Fig. 1b. C. Su ccessive-Cancellation an d F ast-S SC Deco ding The SC decoding algorithm as initially proposed [6] proceed s by visiting the decod er-tree representation—e.g., Fig. 1b—sequen tially , from top to bottom, fro m left to right, successiv ely estimating ˆ u at the lea f nodes, f rom the n oisy channel values. V isiting a left edge (blue) on this rep resen- tation, the SC algorithm can calculate the soft-inp ut LLRs to the child node α l with the min-sum ap p roximatio n [7] α l [ i ] = sgn( α v [ i ] α v [ i + N v / 2 ]) min( | α v [ i ] | , | α v [ i + N v / 2 ] | ) , (2) where α v and N v are respectively the LLRs and node leng th from the parent nod e. At th e root nod e , the chan nel LLRs ar e used. Once a le a f node is reached, a bit ˆ u i (for a non -systematic polar code) is estimated as ˆ u i = 0, when α v ≥ 0 or i ∈ F ; 1, otherwise, (3) where F is the set of frozen-bit indic e s. 1 V isiting a right ed ge ( red), th e LLRs to the child node α r can be calculated [7] as α r [ i ] = α v [ i + N v / 2 ] + α v [ i ], when β l [ i ] = 0 ; α v [ i + N v / 2 ] − α v [ i ], otherwise , (4) where β l is the bit-estimate vector gener ated by th e left sibling in the deco d er-tree. If the left sibling is a leaf n ode, its estimated-bit value ˆ u i is u sed as th e β l . Other wise, the estimed - bit vector β v at a node v is calculated as β v [ i ] = β l [ i ] ⊕ β r [ i ] , when i < N v / 2 β r [ i + N v / 2 ] , otherwise , (5) where β l and β r are the b it- estimate vectors from the left- and right-ch ild n odes, respectively , and ⊕ d enotes a mo dulo-2 addition. Alamdar-Y azdi an d Kschischang pro posed the simplified SC (SSC) algorithm wh ere th e subtrees solely compo sed of e ith er frozen (ra te - 0 codes) or inform ation nodes (rate-1 co des) are not fully traversed [5]. Recogn izing mor e typ es o f constituen t codes, specialized algorithm s an d correspond ing ded ica ted decoder s were prop osed in [ 8]. T he algorithm described in [8], and later extended in [9] an d [1 0], is referred to as the fast- SSC algorith m. Details on the spec ia lize d algorithms of fast- SSC used in this paper are provided alon g side the proposed algorithm in Sectio n II I below . Fast-SSC decoder s have a throug hput that depen d on the frozen-bit lo cations, howe ver it is typically an order of magn itu de high e r than that of other SC-based decoders. Fig. 1 c shows a decoder tree f or th e same ( 8 , 5) po lar code as above where the f ast-SSC algorithm is ap plied, i.e., wher e the tree is prune d by r ecognizin g that the le f t-hand- side subtree of Fig. 1b co rrespond s to th e ML nod e of [8] (T ype- I no de in [10]) and th e right-h and-side subtree to a single-par ity-check (SPC) node. I n Fig. 1c, the former sub tree is replac ed by a purple- striped node and the latter with an or ange-hatc h ed node. D. Succe ssive-Cancellation F lip Decoding The SCF d ecoding alg orithm builds up on a slightly- modified SC decod ing algorithm. It starts by going thr ough a regular SC-decodin g pass (first trial). In parallel to the de- coding pro cess, a list of (absolute) decision LLRs associated to each estimated inform a tion bit is built. Once SC decod ing has completed , the emb e dded CRC is verified. In case it matches, decodin g stops and the estimated co dew ord is outp ut. Oth - erwise, an o ther SC-decoding pass (second trial) is launched, howe ver , this time once the location o f the in f ormation bit that correspo n ds to the least-reliable decision L L R (fro m the first trial) is re ached, that estimated bit is flipped b e f ore resuming SC d ecoding. On ce SC decoding h as c ompleted, the CRC is verified again. If it match e s, the estimated codeword is output otherwise th e process is re started, where th e bit correspon ding to th e second- least-reliable decision LLR is to b e flipp e d. This 1 In the case of a systematic polar code under SC decodin g, the estimated -bit vec tor is obtained at the end of the decodin g process by calculati ng ˆ u N − 1 0 F ⊗ n . process goes o n until the maximum nu m ber of trials T max is reached. Note that setting T max = 1 corresponds to r egular SC decodin g . By na ture, the latency of SCF deco ding is defined a s a multiple of the underlying SC decod er L SCF = T max L SC , (6) where L SC is the latency of the u nderlyin g SC d e coder . Furthermo re, both th e average and worst-case throug hput are f unctions o f the thro ughpu t of that sam e SC decod er . Thus, imp r oving the spe ed o f the u nderlyin g SC decoder also improves the throug hput of the SCF decoder . III. F ast -SSC-F lip D ecoding During the fir st trial, the SCF decoding algor ith m builds a list that co ntains the decision LLRs correspo nding to each informa tio n bits. Th at list λ is used to determ ine which informa tio n bit to flip in su b sequent trials. In th e fo llowing, we show how th e fast-SSC and SCF algorith ms can be merged. The fast-SSC algo rithm uses ded ic a te d decod ers to estimate multiple infor m ation bits at a time. These deco ders need to be modified to calculate th e decision L L Rs required b y the SCF algorithm , and to ad d suppo r t for th e bit-flipp ing pro cedure. These modification s are describ e d in the following subsections for the essential leaf-n ode ty pes (constituent codes) that con- tain inf ormation bits. The other leaf-no de ty pes that ma y be encoun tered can all be e xpressed as node co m binations that include the types covered below . A. Info rmation No des Inform ation nodes hav e length N v and con tain k v = N v informa tio n bits, non e o f their bit locations is frozen. T heir SSC decod ing is a hard d ecision on the n ode soft-inpu t LLRs α N v − 1 0 . As no parity (frozen) bits are inv olved, the calculation of the decision LLRs, λ d , 0 ≤ d < k v , remains the same as in the origin a l SCF algorithm [2] , i.e., as the abso lu te value of each α i , 0 ≤ i < N v λ d = | α d | f or 0 ≤ d < k v , i = d . (7) In case th e decoder has alr eady p assed the fir st tria l, and the in dex of the infor mation bit to be flipped falls within an informa tio n node, after decodin g the rate-1 code, the bit that correspo n ds to that index is flipped. B. Repetitio n Node s Repetition n odes protect a single information bit ( k v = 1) by rep eating it N v times at enco ding tim e . Thus, fast-SSC decodin g takes a hard decision on the sum of the N v node input LL Rs. For the d ecision LLR, the orig inal SCF algorithm uses the absolute value o f the LLR that correspo nds to the informa tio n bit. For a repetition node, both the SC and fast- SSC algorithm s e ff ectively calculate that LLR as the su m of all nod e input LL Rs. Thus, it is propo sed that th e decision LLR be calculated in th e sam e way λ d = N v − 1 X i = 0 α i , fo r d = k v − 1 . (8) After the first trial, if th e index o f the inf o rmation bit to b e flipped corre sp onds to that pro te c te d b y a rep e titio n co de, that bit is flipped after dec o ding. C. Bir epetition Nodes W e define as a birepetition node a node whe r e a ll bit locations are frozen with the e xception of the tw o most- significant positions that carry information b its ( k v = 2) . In the original fast-SSC algorithm [8], birepetition codes of length N v = 4 were dec o ded by the ML n ode, whereas longer birepetition codes were decomp osed. I t was shown in [10] that they can be e ffi ciently decoded b y re cognizing the similarity with repetition n odes, i.e., they ca n be e ffi cien tly decoded as two independ ent repetition codes. The first repetition co de is composed from th e even-indexed location s an d the secon d o ne from the odd- indexed locations. Ther efore, the d ecision-LLR calculations are λ d = N v / 2 − 1 X i = 0 α 2 i + d , fo r 0 ≤ d < k v . (9) Similarly to the r epetition no d e, if the ind ex o f the infor- mation bit to be flipped correspo nds to one of the two bits protected by a birepetition code, the co r respond ing information bit (ev en or od d ind exed) is flipped after decoding. D. SPC Nodes SPC nodes are a special typ e of ( N v , k v ) polar codes with k v = N v − 1, where the only frozen bit is in the first location . A maximu m-likelihood d ecoding algorith m for SPC cod es, when a single estimated-bit vector is to be retain ed, can be summarized as flipping the infor mation bit tha t c o rrespon ds to the least-reliab le input LLR wh en the par ity-check bit is not satisfied [8], [ 11]. The challen ge to adapt this type o f node to SCF deco ding is to calculate with low comp lexity meaning ful alternative decision LLRs th at take into a c count the p arity con straint. Calculating the exact decision LL Rs as the original SCF algorithm would in volved to o m any ca lc u lations. Th us, we propo se an appro ximation similar to the d etection metric update rule for SPC nodes prop osed in [12]. T o this end, we define the decision LL Rs as λ d = | α i | + s ( − 1) p min α N v − 1 0 , fo r 0 ≤ d < k v , i = d + 1 , (10) where s is a scaling factor, and p is the c alculated par ity o n all N v input LLRs, i.e., HD[ i ] = 0 , when α i ≥ 0; 1 , otherwise, and p = N v − 1 M i = 0 HD[ i ] . The approximatio ns on the d ecision LLRs incur an error- correction perform ance lo ss. As will be shown in the next section, this loss can be pa r tially com pensated for by using the scaling factor s b ut, more importantly , it becomes negligible as the maximum nu mber of trials T max is increased. In ca se a b it flip is required , this no de is mor e inv olved than the others as two bit estimates need to be flipped 1 . 5 2 2 . 5 3 3 . 5 10 − 4 10 − 3 10 − 2 10 − 1 E b / N 0 (dB) Frame-erro r rate T max = 8 1 . 5 2 2 . 5 3 3 . 5 10 − 4 10 − 3 10 − 2 10 − 1 E b / N 0 (dB) Frame-erro r ra te T max = 16 SCF [2]: this work: No SPC w / SPC ( s = 1) w / S PC ( s = 0 . 5) SCL: L = 2 L = 4 Fig. 2. E rror-c orrectio n performance comparison for a (512 , 128) polar code decode d using various 16-bit CRC-ai ded SCF-based algorithms with T max = 8 (left) and T max = 16 (right). Curv es for 16-bit CRC-aided SCL decoding with L ∈ { 2 , 4 } included for reference . simultaneou sly f or the par ity con stra int to r emain satisfied. T wo cases c an be distinguished . Let i flip denote the locatio n of the initial bit to be flipp ed, and i min 1 and i min 2 correspo n d to in d ices of the least- and second -least-reliable inpu t LLRs, respectively . If i flip = i min 1 , b oth i flip and i min 2 get flip ped, otherwise, both i flip and i min 1 get flipped. E. Err or -corr ection P erforma nce Fig. 2 compares the err or-correction perfo rmance, in terms of frame-e rror rate (FER), for the new deco ding algo rithm against that of the original SCF algor ithm as pr oposed by [2], where T max is the m aximum n umber o f trials. A cur ve for the new algorithm whe re SPC no des are not used is also included for refer ence. W ithout SPC nodes, SPC codes of length N v = 4 (e.g. , th e node v of Fig. 1c) are decomposed as a length- 2 repetition code comb ined with a leng th-2 rate- 1 code. Lo nger SPC codes genera te a ch ain of rate- R a nd r ate-1 nodes that term in ate with a len gth-2 repetitio n code combin e d with a length-2 rate-1 code. A short (512 , 128 ) polar code is used with a 1 6-bit CRC to b e representative o f what cou ld b e used in next-g eneration m obile-com munication systems [1]. For referen c e , the figure also shows the FER un der 16-bit CRC-aided SCL dec o ding f or list sizes L ∈ { 2 , 4 } . These simulation results are for BPSK-mod ulated ran dom cod ew ords transmitted over an A WGN channel. Comparing the SCF curve (black with aster isk markers) against that of the pro posed algor ith m without SPC no des (cyan with circle markers), either for T max = 8 (left) or 1 6 (right), it can be seen that the FER is v irtually the sam e. Howe ver , as mentio ned in the previous section, the use o f (appro ximate) SPC n odes incu rs a small pe rforman ce loss. Lookin g at the results for T max = 8 (left side of Fig. 2) it can be seen that the loss f or using SPC no d es with a scaling factor s = 1 (p u rple cur ve with tri-star markers) a m ounts slightly more than 0.1 5 dB at a FER of 10 − 3 . Setting s to 0 .5 ( orange curve with diamo nd markers) redu ces th at loss to 0. 1 dB at the same FER. Increasing T max to 16 (right side of Fig. 2) closes the g ap b etween the r e su lts with a nd without the SPC node: at a FER of 10 − 3 , it is of 0.05 d B an d 0.07 dB for s = 0 . 5 and s = 1, respectively . Fig. 2 also shows that, for the simulated (512, 128) polar code, the er ror-correction perfor mance under SCF decodin g is in the vicinity o f SCL decodin g with a list size L = 2 (dashed g reen curve with triangle markers). W e note th at recent work on SCF decodin g [13] pro p oses a low-complexity method, or th ogona l to this work , where the er ror-correction perfor mance for low-rate po lar co des of length N = 102 4 was shown to improve by appr oximately 0.2 5 dB. IV . H ardw are I mplement a t ion C onsidera tions As in [3], the lis t of decision LL Rs λ can be kept sorted with an insert-sort unit, ru nning in parallel with the decodin g process, capable of hand lin g a maximum of m in( P − 1 , T max − 1 ) input LLRs, wher e P is the maximum num ber of LLRs that specialized decod e rs can simultaneou sly access fro m m e m ory . By keeping the list so r ted, its size c a n be co n strained to T max − 1. Thus, a m emory of Q λ ( T max − 1 ) bits is su ffi cien t to store the de c isio n -LLR list, wh ere Q λ is the numb er of quantization b its used to represent d e cision LL Rs. Alongside, a list of the correspon ding in dices requ ires a memory of ( T max − 1 ) log 2 k bits. Starting with the implementation of the fast-SSC algo- rithm a s descr ibed in [8], the ML unit—an unrolled gener ic SC deco der for len gth-4-o nly birep etition codes—would b e replaced with a second co py of th e unit im p lementing the repetition node in o r der to implement the Birepetition node . If P > T max − 1, the SPC unit would ne e d an LLR so rter to only retain the T max − 1 smallest decision LLRs. Some bit-flip ping circuitry n eeds to be add ed to all un its hand ling info rmation bits. Th ese modification s are expected to h av e little impact o n the critical pa th as even the most inv olved mod ifica tio ns (SPC unit) only a p pends bit flips, the remainder of the calculations can occur in pa rallel. Latency Comparison The o nly re ported h a r dware implem entation of an SCF decoder [ 3] is built upo n a slightly impr oved semi-p arallel SC decoder with a latency , in clock cycles (CCs), defined as L SC = 2 N + N 64 log 2 N 256 − log 2 N X i = 0 $ b 2 i % & 2 i 64 ' , (11) where N is the polar-code length , and b is the locatio n of th e first information bit. The la ten cy of the fast-SSC algor ithm canno t be expressed in comp act closed form a s it heavily depend s o n the froze n-bit locations, a n d n ode ty pes an d co nstraints. Howev er, numer ic a l ev aluations show that it is ro ughly an or der of magn itude lower than that o f SC decoding for all relevant c ode rates. 10 0 10 − 1 10 − 2 10 − 3 10 − 4 10 2 10 3 10 4 T = 8 [3] T = 16 [3] T = 8 (this work) T = 16 (this work) Frame-erro r rate A verage Execu tion Time (CCs) T max = 8: [3] this work T max = 16: [3] this work Fig. 3. A ve rage decoding-e xec ution time for a (512 , 128) polar code decoded with 16-bit CRC-aided SCF-based algorit hms. For this work, s = 0 . 5. T o get a grasp of the impr ovements under reasonab le condition s, Fig. 3 shows a com parison of the average execution time, in terms o f clock cycles, between the SCF decod e r of [3 ] with wha t could b e that o f the propo sed fast-SSC-flip decoding algorithm . For this work, all the original nod es fro m [8] were used excep t th e ML node which has b een r e placed with the more e ffi c ie n t Birepetition n o de. The Repetition , Birepetition, and SPC nodes are constrained to a maximu m size of 32, 64, and 64, respectively . The value of P is set to 64 to match that of [3]. All curves ar e for the same cod e used in Fig. 2. Th e scaling factor s of (10) was set to 0.5. Fig. 3 confir ms that the average execution time o f the propo sed fast-SSC-flip algo rithm is close to an o rder of magnitud e lower than that of the other work , both for T max = 8 (solid curves) and T max = 16 (dashe d curves). Furthermo re, it can be seen that the worst-case execution time for this work with T max = 8 (solid red bottom -most line) is o nly slightly worse that th a t of the best-case execution tim e of [3]. V . C onclusion In this pap er , we showed how to merge the state-of-th e - art high-spee d SC-based decodin g algorith m—fast-SSC—with the SCF algor ithm. The resultin g algo r ithm was shown to have a significantly h igher speed th an th e SCF-decoder imp lem en- tation fro m the literature while retaining an error-correction perfor mance very clo se to the o riginal SCF algorithm . The key ingr e d ients are the new dec ision-LLR calcu lations and bit-flipping p rocedu res introduce d to SCF d ecoding f or the multi-bit dedicated decoders u sed in the fast-SSC algorithm . The p roposed dec o ding alg o rithm is prom ising for a p pli- cations that can hand le a variable execution time. Its error- correction performanc e can match that of list-based d ecoding with a small list an d its speed ten ds to th at of the fastest low- complexity SC dec o ders in p r actical op erating conditions. A cknowle dgement The au thors would lik e to thank Or io n Afisiadis of EPFL for the helpful discussions. This w ork has been supported by the Swiss National Scien ce F ounda tio n unde r grant #17 5813. R eferences [1] MCC Support, “Fi nal Report of 3GPP TSG RAN WG1 #87 v1.0.0, ” Feb 2017. [Online]. A vai lable: http: // www .3gpp.org / ftp / tsg ran / WG1 RL1 / T SGR1 88 / Docs / R1- 170 1552.zip [2] O. Afisiadis, A. Balatsouk as-Stimming, and A. Burg, “ A lo w-comple xity improv ed successiv e cancellat ion decoder for polar codes, ” in Asilomar Conf . on Signals, Syst., and Comput. , Nov 2014, pp. 2116–2120. [3] P . Giard, A. Balat soukas-Stimming, T . C. M ¨ uller , A. Bonett i, C. Thibeault, W . J. Gross, P . Flatresse, and A. Burg, “Polarbear: A 28-nm FD-SOI ASIC for decoding of polar codes, ” IEEE T rans. Emerg . Sel. T opics Circ uits Syst. , vol. PP , no. 99, Feb 2017. [4] I. T al and A. V ardy , “How to construct polar codes, ” IEEE T rans. Inf. Theory , vol. 59, no. 10, pp. 6562–6582, Oct 2013. [5] A. Ala mdar-Y azdi and F . R. Kschisc hang, “ A simpl ified successi ve- cance llation decoder for polar codes, ” IEEE Commun. Lett. , vol. 15, no. 12, pp. 1378–1380, Dec 2011. [6] E. Arıkan, “Channel polariza tion: A method for constructi ng capa city- achie ving codes for symmetric binary-in put memoryless channels, ” IEEE T rans. Inf. Theory , vol. 55, no. 7, pp. 3051–3073, Jul 2009. [7] C. Leroux, I. T al, A. V ardy , and W . Gross, “Hardware archite ctures for successi ve ca ncella tion deco ding of polar codes, ” in IEEE Int. Conf. on Acoustics, Speech, and Signal Process. (ICASSP) , May 2011, pp. 1665–1668. [8] G. Sarkis, P . Giard, A. V ardy , C. T hibeault, and W . J. Gross, “Fast polar decode rs: Algorithm and implement ation, ” IEEE J. Sel. A re as Commun. , vol. 32, no. 5, pp. 946–957, May 2014. [9] P . Giard, A. Balatsouk as-Stimming, G. Sarkis, C. Thibeault, and W . J. Gross, “Fast low-c omplexi ty decoders for lo w-rate polar codes, ” Spring er J. Signal Proce ss. Syst. , vol. PP , Aug 2016. [10] M. Han if and M. Arda kani, “F ast succ essi ve-ca ncella tion de coding of polar codes: identific ation and decoding of ne w nodes, ” IEEE Commun. Lett. , vol. PP , no. 99, Aug 2017. [11] R. Silv erman a nd M. Balser , “Coding for constant- data-rat e systems, ” T rans. IRE Prof . Group Inf. Theory , vol. 4, no. 4, pp. 50–63, Sep 1954. [12] P . Giard, A. Bala tsoukas-Stimming, and A. Burg, “B lind detecti on of polar codes, ” in IEEE Int. W orkshop on Signal Proce ss. Syst. (SiPS) , Oct 2017, to appear . [Online]. A vail able: https: // arxi v . org / abs / 1705.02111 [13] C. Condo, F . Ercan, and W . J. Gross, “Improv ed s uccessi ve cancel lation flip decoding of polar codes based on error distrib ution, ” in IEEE W irele ss Commun. and Netw . Conf. (WCNC) , 2018, pp. 1–6, to appear . [Online]. A v ailabl e: http: // arxi v .org / abs / 1711.11096

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment