An SDR Implementation of a Visible Light Communication System Based on the IEEE 802.15.7 Standard

The aim of this paper is to present an implementation of a functional IEEE 802.15.7 real-time testbed based on the Software Defined Radio (SDR) concept. This implementation is built with low cost commercial off-the-shelf (COTS) analog devices and the…

Authors: Jorge Bar, a, Pol Henarejos

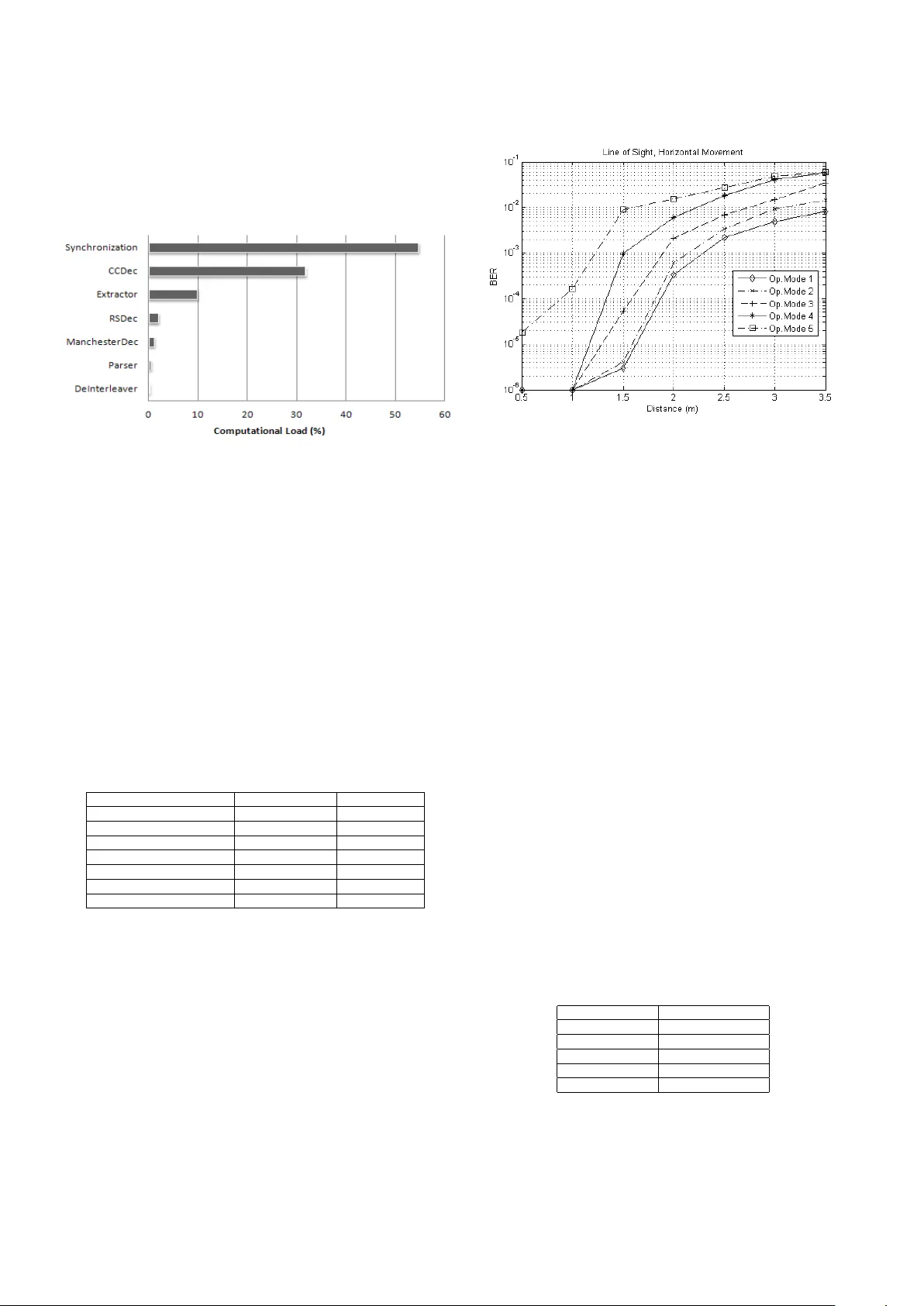

1 An SDR Implementation of a V isible Light Communication System Based on the IEEE 802.15.7 Standard Jorge Baranda ∗ , Pol Henarejos ∗ , Ciprian G. Gavrincea ∗ ∗ Centre T ecnol ` ogic de T elecomunicacions de Catalunya (CTTC), Castelldefels, Barcelona (Spain) Email: { jorge.baranda, pol.henarejos, ciprian.ga vrincea } @cttc.es Abstract —The aim of this paper is to pr esent an implementa- tion of a functional IEEE 802.15.7 real-time testbed based on the Software Defined Radio (SDR) concept. This implementation is built with low cost commercial off-the-shelf (CO TS) analog de- vices and the use of Uni versal Softwar e Radio P eripheral version 2 (USRP2) equipment combined with a generic object-oriented framework that takes advantage of several open sour ce softwar e libraries. The prototype is validated in a contr olled laboratory en vironment with an over -the-air measur ement campaign. I . I N T RO D U C T I O N V isible Light Communications (VLC) is an emerging re- search field of free space optic (FSO) communications. The ev olution of high-power white light emitting diodes (LEDs) within the last decades has led to the de velopment of low cost lighting devices with better performance in terms of both energy efficienc y and life expectancy . LEDs are expected to replace incandescent light bulbs and fluorescent lamps in the next generation illumination systems. Nonetheless, these devices can be used for applications beyond the illumination purpose [1]. The use of a LED to transmit data while serving as an illumination source has captured the interest of the research community as well as global standardization ef forts [2]. The use of VLC technology presents many attractiv e ad- vantages in terms of av ailable bandwidth, non-interference with radio bands (critical especially due to the scarcity in some frequency bands such as ISM), potential spatial reuse, inherent protection against eavesdropping and, all of this with power efficient devices and without high deployment costs. In the last years, the focus of the research community has been centered in improving the data rates achiev able by VLC sys- tems, obtaining performances of 1.25 Gb/s [3]. Nevertheless, although there are some standards already published for VLC communications ([4], [5]), proof-of-concept implementation examples based on these standards are scarce. In this paper , we present, to the best of our knowledge, the first implementation of a real-time VLC system prototype based on the IEEE 802.15.7 specification [5] using low cost CO TS analog devices. F or this dev elopment, we have follo wed an SDR based design approach, similar to the one presented in [6]. The SDR based approach brings a lot of advantages to de- velop communication system testbeds, regarding a pure hard- ware (HW) based implementation. Among them, we would like to highlight: flexibility , modularity , reduced financial costs and shorter dev elopment time. These advantages are due to the fact that, in an SDR-based implementation, hardware problems are turned into software problems, allo wing the use of nov el algorithms almost immediately , accelerating the transition from simulation to demonstration. From the v ariety of a v ailable commercial SDR platforms [7], we find attractive the equipment provided by Ettus Research [8], specially the USRP2 and its predecessors, because of its superior trade- off between price and performance and, the support provided by a large user community . Finally , this paper un veils the performance of the de veloped VLC system with an over -the- air measurement campaign. I I . I E E E 8 0 2 . 1 5 . 7 P H Y L A Y E R B R I E F O V E RV I E W The IEEE 802.15.7 standard [5] defines the physical (PHY) and the medium access control (MA C) layer for short-range optical wireless communications using visible light for indoor and outdoor applications. One of its main distinguishing points compared to other specifications, such as the Japan Electronics and Information T echnology Industries (JEIT A) specifications [4], is the support for dimming and flickering mitigation techniques [9]. These aspects are very important due to the negati ve physiological effects that flickering may hav e in humans and because dimming allo ws power sa vings and ener gy efficienc y . The standard presents three different PHY layers which are grouped by their data rates. The operation range of PHY I is from 11.67 kb/s to 266.6 kb/s, PHY II data rates are comprised between 1.25 Mb/s and 96 Mb/s, while PHY III operates from 12 Mb/s to 96 Mb/s. The modulation formats are different among PHY I/II and PHY III. While PHY I and PHY II use on-off ke ying (OOK) and v ariable pulse-position modulation (VPPM), PHY III uses a particular modulation format called color shift ke ying (CSK), in which information is transmitted by means of multiple optical sources. Each PHY mode includes run length limiting (RLL) codes to achiev e direct current (DC) balance, av oiding data induced flickering, and forward error correction (FEC) schemes to improv e the link reliability for the envisaged en vironments. PHY I is optimized for low data rate, transmissions over long distances, e.g., outdoor applications such as traffic and vehicle lights; and PHY II/III are designed for high data rate indoor point-to-point applications. FEC schemes proposed by 2 the standard are a combination of Reed-Solomon (RS) and con volutional codes (CC). These schemes work reasonably well in the presence of hard-decisions performed by the clock data recovery circuits (CDR) and make the interf ace with the proposed RLL codes (Manchester , 4B6B and 8B10B) easier . I I I . D E V E L O P M E N T M E T H O D O L O G Y The de velopment of this prototype started with the imple- mentation of a reference encoder-decoder model in MA TLAB according to the specifications of [5] for PHY I/II operating modes. Regarding the MAC layer, only a set of features of the header specification are included to simplify the communica- tion link. The construction of the model was useful for a better understanding of the specification and constituted an important debugging tool which helped in the posterior implementation under the FlexiCom object-oriented framework. FlexiCom framework is born as an evolution of the uP- HYLA framew ork [10]. As uPHYLA, Fle xiCom frame work is intended as a tool to implement in softw are the physical layer of any communication system. Hence, a practical demonstra- tion of no vel signal processing and communication algorithms with real digitized signals can be performed within a short dev elopment time. Nevertheless, the ne w created architecture for the FlexiCom frame work provides enhanced graphical capabilities and simplicity to users and dev elopers, as depicted in Fig. 1. Fig. 1. Graphical Interface used to configure the VLC communication layout. FlexiCom platform uses Nokia’ s Qt library [11] to offer the possibility of choosing among a set of communication system layouts. Each layout presents a customized interface for system configuration and performance metric visualization. Moreover , this framework runs over most operating systems (OS) such as W indows, Linux or Mac OSX. Once the system is configured, FlexiCom uses the GNU Radio library [12] to construct the communication system and to distribute the samples among the in volv ed blocks in a continuous flo w . In the second dev elopment phase, the MA TLAB code is ported to the FlexiCom framew ork. Due to the stream-based flow of samples in the GNU Radio en vironment, the effort is focused on redesigning the encoder/decoder chains, identifying the minimal processing units and introducing low-comple xity algorithms which improve the system latenc y . Finally , we would like to highlight the importance of the testing phase to verify the successi ve de velopment steps. In the MA TLAB programming step, the e xhaustive test of all possible combinations allo ws the functional verification of the encoder and the decoder implementation. Moreover , the information provided by this initial testing phase helps to accelerate the multi-lev el testing phase (basic block unit testing, module testing and system testing) of the implementation under the FlexiCom framework by means of the CppUnit testing frame- work [13]. I V . S Y S T E M M O D E L The current prototype implementation supports the modu- lation and demodulation of all the operating and data modes defined for PHY I at [5], both for OOK and VPPM schemes. These modes are included in T able I. Based on the SDR approach used in this implementation, the prototype is divided into two main subsystems: hardw are and software subsystem, as shown in Fig. 2. The hardware subsystem is constituted by the elements labeled as LED, Photodiode, USRP TX and USRP RX, while the software subsystem is composed by the elements labeled as FlexiCom TX and Fle xiCom RX. T ABLE I P H Y I O PE R A T I N G M O D ES Modulation RLL Optical FEC Data Operating Code clock rate Outer Code (RS) Inner Code (CC) Rate mode OOK Manchester 200 KHz (15,7) 1/4 11.67 kb/s 1 (15,11) 1/3 24.44 kb/s 2 (15,11) 2/3 48.89 kb/s 3 (15,11) none 73.3 kb/s 4 none none 100 kb/s 5 VPPM 4B6B 400 KHz (15,2) none 35.56 kb/s 1 (15,4) none 71.11 kb/s 2 (15,7) none 124.4 kb/s 3 none none 266.6 kb/s 4 A. Hardwar e Subsystem The analog transmitter front-end is constituted by the USRP2 platform equipped with the LFTX daughterboard, an amplification stage, the LED driv er circuit and a commercial high po wer white LED as the light emitting source. The software subsystem generates the stream of bits which are digital to analog (D AC) con verted in the USRP2. The modulated signal provided by the SDR platform is amplified to be adjusted to the le vels required to control the LED dri ver circuit. This circuit is composed of a po wer MOSFET transis- tor (STD12NF06L) which acts in switching mode, providing the needed current to the LED fixture. The light source is a commercial phosphorescent white LED module (OST AR R LE CW E2B), consisting of a blue LED covered by a yello w phosphor layer designed for indoor lighting applications. The light source is equipped with a reflector that reduces the 3 viewing angle of the LED and concentrates the light beam. W ith the current reflector , the viewing angle is reduced to 30 ◦ (half optical transmitted power is achiev ed at 15 ◦ from the axis of the LED de vice). Fig. 2. IEEE 802.15.7 based VLC Prototype. The analog receiv er front-end is constituted by the USRP2 device equipped with the LFRX daughterboard and a commer- cial photodetector (THORLABS R PD A36A) equipped with a spherical concentrating lens. The detector consists of a PIN sil- icon photodiode with an activ e area of 13 mm 2 and an optical sensitivity of 0.2-0.4 A/W in the visible range. The PD A36A device is equipped with a transimpedance amplifier (TIA) chain circuit with manual adjustable gain, ranging between 0 and 70 dB. This setting impacts in the recei ver bandwidth. But this is not the only bandwidth limiting factor of this setup. Beside the limitations of the LED fabrication process [14], the high amount of current that is required to operate ( ∼ 700 mA) conditions the switching speed possibilities of the led driv er circuit. B. Software Subsystem The software subsystem is constituted by tw o general pur- pose processors (GPPs), one for the modulation and one for the demodulation of the signals. An IEEE 802.15.7 frame is composed of three elements: the synchronization header (SHR), the physical header (PHR) and the physical service data unit (PSDU). In order to maintain the lev el of luminance and to av oid inter-frame flickering, an in-band idle pattern is inserted between frames [9]. The SHR contains the fast locking pattern (FLP) and the topology dependent pattern (TDP), used to lock the CDR circuit and perform the synchronization with the incoming message. The PHR contains frame information related to the length of the data unit, the used modulation and FEC scheme. The PSDU is the data unit, and also contains the MA C Header (MHR) in which parameters such as the sequence length and control format fields are included. As the current implementation features a broadcasting system, it modulates/demodulates the MHR headers according to the format specified in [5] for data frames. The building blocks of the physical layer transmitter and receiv er are depicted in Fig. 3 and Fig. 4, respectiv ely . Fig. 3. Structure of the VLC IEEE 802.15.7 software transmitter . At the transmitter , the PHR and the PSDU units are gen- erated independently according to the system configuration. Each unit passes through a PHY I modulator block, where the corresponding FEC scheme and RLL coding are applied (see T able I). After the modulation, both units are assembled into one stream of data and the TDP pattern is inserted. In the last block, before the USRP2 device, the FLP pattern and the idle pattern are attached to form the entire frame. Fig. 4. Structure of the VLC IEEE 802.15.7 software receiver . At the recei ver , frame synchronization and timing recov ery are performed at the first block. Frame recov ery is achieved through the exploitation of repeated patterns at the SHR header . Timing recovery is the procedure to determine the optimum sampling instant required to decide the value of the incoming bits. Due to the limitations of the USRP2 hardware in terms of clock reconfigurability , timing reco very is performed using a non-data aided detector based on the maximum likelihood (ML) algorithm [15]. According to this detector , the optimum sample corresponds to the one that maximizes the ener gy of the received oversampled sequence of samples. As this prototype works with a binary modulation, many transitions are produced within a frame. The ov ersam- pling allows a better reconstruction of the wa veform, so the transitions can be easily detected through the maximum ener gy criterion. Both algorithms hav e a limited complexity , allowing a feasible implementation in terms of system latency . Moreover , the support of V ector-Optimized Library of K ernels (VOLK) inside the GNU Radio library allo ws the use of Streaming SIMD Extensions (SSE), which boosts the execution of the synchronization block by a factor of four . Once the incoming flow of bits is synchronized, the PHR and the PSDU units are extracted and demodulated according to the system configura- tion. Finally the bits are parsed in order to extract the informa- tion corresponding to the different units and the validity of the receiv ed frame is checked. A frame is declared in v alid if there is an error in the cyclic redundanc y check (CRC) field, or the frame sequence number does not correspond to the previous frame. Fig. 5 shows the distribution of the relative computational load among the receiving processing blocks obtained with the OProfile tool [16] when using Operation mode 1 and OOK modulation, which is the more demanding operating mode in terms of computer processing. The execution of 4 the receiving chain requires only 25% of the total computer processing power . The synchronization block represents 55% of the processing, while the demodulation (Manchester + CC + RS decoding + Deinterleaver operations) accounts for the 35%. The remaining 10% is required to extract the PHR and the PSDU bit streams and to parse the information included within these units. Fig. 5. Distribution of the computational load among the different recei ving processing blocks. V . R E S U LT S Once all the system units are tested and validated indi- vidually , the last phase of the development is dedicated to characterize the performance of the complete implementa- tion (baseband modulation/demodulation, signal conditioning (D AC/ADC) and analog optical front-ends) using over -the-air measurements in a controlled environment. The transmitter code runs in a PC laptop with 2 GB of RAM and an Intel Core 2 Duo I3 processor clocked at 1.5 GHz. The receiver code runs in a PC laptop with 4 GB of RAM and an Intel Quad-core I5 processor clocked at 2 GHz. Additional details of the test-system are summarized in T able II. T ABLE II T E ST B E D S Y S TE M D E TA IL S Feature T ransmitter Receiv er Operating System W indows 7 H.E. Ubuntu 12.04 Platform FlexiCom FlexiCom QT V ersion 4.8 4.8 GNU Radio V ersion 3.6.2 3.6.2 USRP2 HW revision 4 4 USRP2 Firmware version 3.0.4 3.0.4 Daugtherboard model LFTX LFRX In the first experiment, measurements are taken in a medium-sized room without windows where the transmitter and the receiv er are horizontally aligned and separated in order to determine the system bit-error rate (BER) performance versus the distance. In this setup, the transmitter is moved in 50 cm steps and, at least, 50000 frames of 128 bits of data are transmitted to measure the system performance. The amplification of the TIA chain at the receiv er is set to 0 dB. The BER performance versus distance for each operating mode of the PHY I specification using OOK modulation is presented in Fig. 6. The points presenting a BER value of 10 − 6 means that no error was found during the test. 10 − 6 constitutes the floor of our measurement because the amount of transmitted bits in each repetition is in the order of 10 6 . Fig. 6. Performance of the VLC IEEE 802.15.7 prototype for different operating modes of PHY I using OOK modulation. Prior to analyze the performance of the system, a comment about the tested distances is w orthy to be done. According to Section II, PHY I is thought to be used for outdoor applica- tions. In such scenarios, the light emitter is constituted by an array of LED de vices, which are capable of providing much more luminous flux than the current setup herein presented. One must remember that the current setup uses a single luminary with a maximum output of 450 lumens, according to its datasheet, which is suitable for indoor illumination systems. As expected, the system performance degrades with the distance as a consequence of a lower SNR value at the receiv er site. Operation mode 1 and 2, which present the strongest channel coding schemes among the considered op- erating modes (see T able I), obtain the best performance. Nonetheless, as the distance between the transmitter and the receiv er increases, the impact of channel coding in less robust schemes disappears and the BER performance becomes almost equiv alent to the scheme without channel coding scheme (Op. mode 5), impacting in the achie ved effecti ve data rate. W e define the effecti ve data rate as the total amount of correct information bits receiv ed without taking into account the ov erhead introduced by the different headers (SHR, PHR and MHR) and the idle-pattern. T able III shows the measured effecti ve data rate for each considered operating mode using OOK modulation at a distance of two meters. T ABLE III M E AS U R E D E FF EC T I V E DAT A R A T E AT 2 ME T E RS D IS TA NC E Operating Mode Effecti ve data rate Op. Mode 1 7.9 kb/s Op. Mode 2 18.01 kb/s Op. Mode 3 24.63 kb/s Op. Mode 4 32.38 kb/s Op. Mode 5 35.22 kb/s In the second experiment, we tested the end-to-end per- formance of our prototype when transmitting and receiving 5 a video coded in MPEG-TS (T ransport Stream) format in a medium-sized office room with standard illumination condi- tions. The transmitter extracts the information from an MPEG- TS stream coded at an MPEG2 video compression bit rate of 25 kb/s and audio rate of 16 kb/s, and modulates it according to the frame structure explained in Section IV -B using the coding scheme corresponding to 73.3 kb/s of data rate (see T able I). At the receiv er side, the data payload is demodulated and sent through a user data protocol (UDP) socket connection to the V ideoLAN streaming software [17]. Additionally , the system clock data rate is set to 500 KHz, 2.5 times faster than the IEEE 802.15.7 specification of PHY I OOK modulation in order to cope with the extra signaling of the MPEG stream and to achiev e on-line displaying. The current prototype implementation supports the on-line streaming at a distance of around 1.5 m with an effecti ve measured data rate of about 107 kb/s with a packet error rate (PER) of 1e-3. In this setup, the amplification of the TIA chain at the recei ver is set to 20 dB. Fig. 7 presents one captured image from the receiv ed video signal, together with some metrics captured with the FlexiCom framework: effecti ve data rate, number of total/lost packets, packet error rate (PER) and quantity of correct/incorrect decoded packets (PHR and PSDU units). Fig. 7. Receiv ed video capture, for a 1.5m link (from “Gangnam Style”, PSY , 2012). V I . C O N C L U S I O N S A N D F U T U R E W O R K W e hav e presented a functional system prototype imple- menting all the operating modes of the PHY I specification of the IEEE 802.15.7 standard for VLC. This development is based on the SDR concept, providing the prototype with enough flexibility and modularity to enhance its capabilities without requiring long development time and high financial costs. The prototype is completed with lo w cost COTS analog devices to perform the transmission and reception of the light signal. The IEEE 802.15.7 standard serves as a promising platform to start developing and introducing VLC solutions into the market for lo w-medium data rate point-to-point and broadcast systems in the field of intelligent transportation systems (ITS) or smart indoor locating (SIL). Future system dev elopment will be focused on two aspects: a) the integration of dimming functionalities into the commu- nication framework when using OOK modulation by inserting compensation symbols within the frame without reducing the range of the communication system; and b) further research into the analog subsystem to improv e the system bandwidth and to implement the operating modes of PHY II. From the software point of view , the MA TLAB simulator and the FlexiCom modules are easily customizable. A C K N O W L E D G M E N T The authors would like to thank Miquel Payar ´ o, Christian Ibars and the Access T echnologies area members of CTTC for their support for the implementation of the VLC system prototype. R E F E R E N C E S [1] T . K omine and M. Nakagawa, “Fundamental Analysis for V isible-Light Communication System using LED Lights”, IEEE T ransactions on Con- sumer Electr onics , vol. 50, no. 1, pp. 100-107, Feb. 2004. [2] J. V ucic and K.-D. Langer, “High-Speed V isible Light Communications: State-of-the-Art”, in Optical F iber Communication Confer ence (OFC’12) , Los Angeles, USA, Mar . 2012, OSA T echnical Digest (Optical Society of America, 2012). [3] C. Kottk e, J. Hilt, K. Habel, J. V ucic and K.-D. Langer , “1.25 Gbit/s V is- ible Light WDM Link Based on DMT Modulation of a Single RGB LED Luminary”, in Proc. Eur opean Confer ence on Optical Communications , Amsterdam, The Netherlands, Jun. 2012, OSA T echnical Digest (Optical Society of America, 2012). [4] Japan Electronics and Information T echnology Industries Association (JEIT A), V isible Light Communication CP-1221, CP-1222 specifications, Japan, 2007. [5] Institute of Electrical and Electronics Engineers, “Standard for Local and metropolitan area networks, Part 15.7: Short-Range Wireless Optical Communication Using V isible Light”, Rev . 802.15.7-2011, 2011. [6] M. Rahaim, T . Borogov ac, T .D.C. Little, A. Mirvakili and V . Joyner , “Demonstration of a Software Defined V isible Light Communication System”, in Demo and Exhibits of International Confer ence on Mobile Computing and Networking , Las V egas, USA, Sep. 2011. [7] R. Farrell, M. Sanchez and G. Corley , “Software-Defined Radio Demon- strators: An Example and Future T rends”, International Journal of Digital Multimedia Broadcasting , vol. 2009, Article ID 547650, 12 pages, 2009. doi:10.1155/2009/547650. [8] Ettus Research LLC, “Univ ersal Software Radio Platform” [Online]. A vailable: http://www .ettus.com , Retrieved: March 11, 2013. [9] R.D. Roberts, S. Rajagopal and S.-K. Lim, “IEEE 802.15.7 Physical Layer Summary”, GLOBECOM W orkshops, 2nd IEEE W orkshop on Optical W ireless Communications , Houston, USA, Dec. 2011, pp. 772-776. [10] J.Baranda, P .Henarejos, Y .Grunenberger , and M. N ´ ajar , “Prototyping with SDR: a quick way to play with next-gen communications sys- tems”, International Symposium on W ireless Communication Systems (ISWCS’11) , Aachen, Germany , Nov . 2011, pp.16-20. [11] “QT Homepage” [Online]. A vailable: http://qt.nokia.com/products/ , Re- triev ed: March 11, 2013. [12] “GNU Radio, the GNU Software Radio project” [Online]. A vailable: http://gnuradio.or g/redmine/pr ojects/gnuradio/wiki , Retriev ed: March 11, 2013. [13] “CppUnit Project Page” [Online]. A vailable: http://sour cefor ge.net/pr ojects/cppunit/ , Retriev ed: March 11, 2013. [14] J. V ucic, C. Kottke, S. Nerreter, A. Bttner, K.-D.Langer, and J.W . W ale wski, “ White Light Wireless T ransmission at 200+ Mb/s Net Data Rate by Use of Discrete-Multitone Modulation”, IEEE Photon. T echnol. Lett . vol.21, no. 20, pp. 1511-13, Oct. 2009. [15] U. Mengali and A.N. D’Andrea, “ Synchronization T echniques for Digital Receivers ”, Plenum Press, NY , 1997. [16] “OProfile Homepage” [Online]. A vailable: http://opr ofile.sourcefor ge.net/news/ , Retrieved: March 11, 2013. [17] “V ideoLAN Homepage” [Online]. A vailable: http://www .videolan.or g/index.html , Retrieved: March 11, 2013.

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment