A Ternary Digital to Analog Converter with High Power Output and 170-dB Dynamic Range

A prototype of a very high dynamic range 32-bits Digital to Analog Converter (DAC) was designed and built for the purpose of direct auditory stimulus generation. It provides signals from less than 100 nV up to 50 Watts peak power output, driving a 32-Ohms earphone or speaker. The use of ternary cells makes possible a 170 dB dynamic range that is basically limited by thermal noise only.

💡 Research Summary

The paper presents the design, implementation, and experimental validation of a novel digital‑to‑analog converter (DAC) that achieves an unprecedented dynamic range of approximately 170 dB while delivering up to 50 W of peak power into a 32‑Ω load. The motivation stems from audiometry requirements: to generate acoustic stimuli from the hearing threshold (≈ –10 dB SPL) up to discomfort levels (≈ 120 dB SPL) and to accommodate additional head‑phone‑specific gain variations, short‑duration loudness boosts, and higher‑quality ear‑phone inefficiencies. Conventional DACs, even high‑performance sigma‑delta devices, are limited to about 130 dB dynamic range, and any subsequent power amplification inevitably adds noise, preventing a truly “single‑stage” solution.

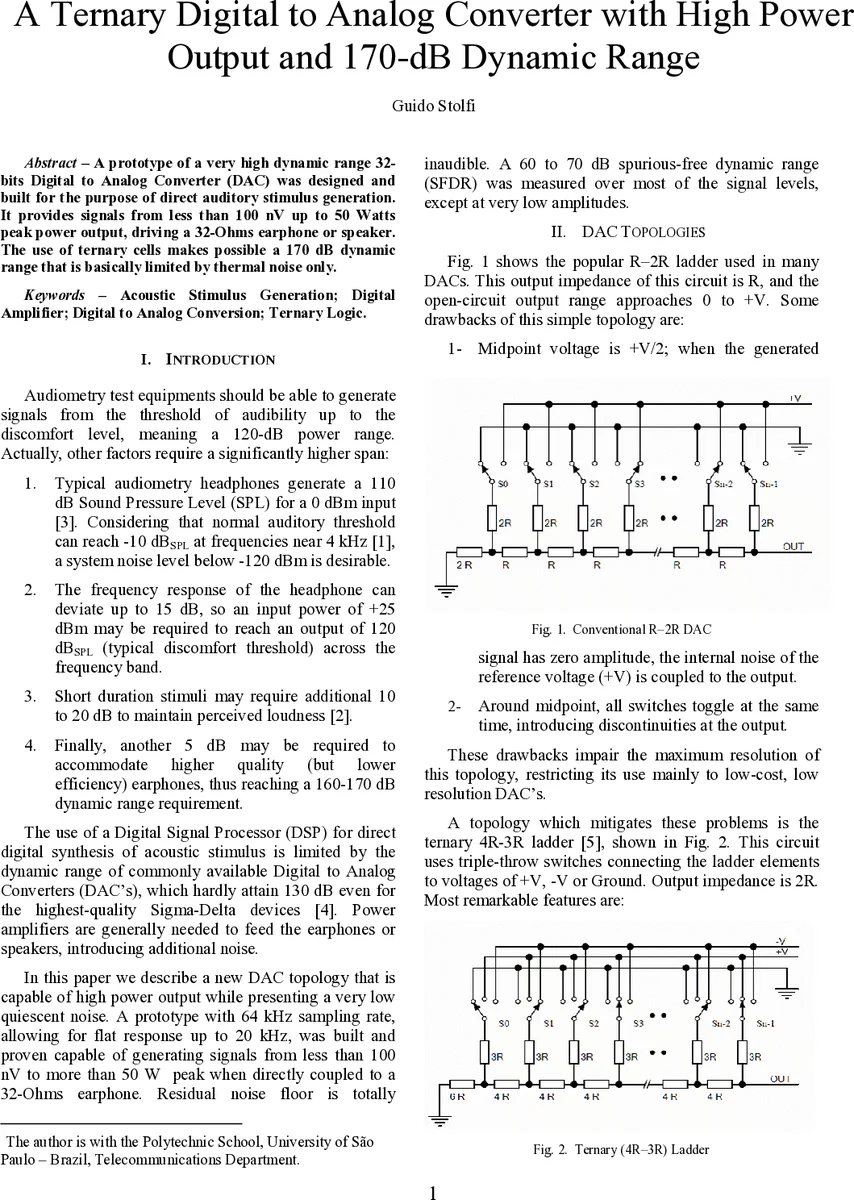

To overcome these limitations, the authors adopt a ternary (4R‑3R) ladder architecture instead of the classic binary R‑2R ladder. In the ternary ladder each node can be connected to +V, –V, or ground via a triple‑throw switch, which yields a constant output impedance of 2R, eliminates the mid‑scale V/2 reference noise coupling, and reduces discontinuities because switches toggle sequentially rather than simultaneously. The theoretical quantization noise of a 32‑bit (20‑stage ternary) converter corresponds to a 190.8 dB dynamic range; practical constraints (5 % resistor tolerances, switch non‑idealities) lower the measured spurious‑free dynamic range (SFDR) to 60‑70 dB, still well above typical headphone harmonic distortion (≈ 30 dB).

The hardware implementation consists of 20 ternary stages divided into three groups: six high‑voltage “power‑of‑3” weighted stages, six high‑voltage regular ladder stages, and eight low‑voltage ladder stages. High‑voltage stages are driven from a 90 V supply using MOSFET half‑bridge drivers, allowing the DAC to swing up to ±180 Vpp (≈ 42 Vrms) and deliver 50 W into 32 Ω for short bursts. Low‑voltage stages operate at 12 V with 15–20 kΩ resistors, minimizing electromagnetic coupling and stray capacitance that would otherwise dominate the noise floor at nanovolt levels. Aluminum shielding serves both as a heat sink and as EMI protection.

Control logic resides in a DSP that generates 32‑bit fixed‑point samples. A sequential conversion algorithm maps these samples to 20 ternary digits, which are then sent via a serial‑to‑parallel interface: 16 bits to the high‑voltage modules (4 bits per module) and 8 bits to the low‑voltage module. The design deliberately uses low‑power resistors and modest heat‑sinking because the DAC is intended for short‑duration bursts rather than continuous full‑power operation.

Measurements confirm the design goals. With a 64 kHz sampling rate the DAC exhibits a flat frequency response up to 20 kHz. Power efficiency peaks at about 30 % when the output is roughly –10 dB below maximum. The noise floor reaches the thermal limit (kTB ≈ –131 dBm), and a 60 nV burst (–177 dBFS) is observable on a digital oscilloscope after averaging. SFDR measurements using an HP 3561A analyzer show 60‑70 dB across most output levels; the degradation at the lowest amplitudes is attributed to the use of standard 5 % resistors rather than precision matched parts.

In conclusion, the authors demonstrate that a ternary ladder DAC combined with a dual‑voltage stage architecture can simultaneously provide high power output and an ultra‑wide dynamic range, fulfilling the stringent requirements of audiometric testing and opening possibilities for any application demanding analog signals with >150 dB of dynamic range. Future work is suggested to improve resistor matching and switch linearity to push SFDR closer to the theoretical limit.

Comments & Academic Discussion

Loading comments...

Leave a Comment