RISC and CISC

RISC와 CISC는 컴퓨터 아키텍처 설계에서 두 가지 극단적인 접근 방식을 대표하며, 각각이 특정 시점에서의 기술적 요구사항과 제한 조건에 따라 발전해왔습니다. 이 논문은 RISC와 CISC의 장단점을 비교하고 현대 컴퓨팅 환경에서의 적합성을 분석합니다. 1. 설계 철학의 배경 CISC 아키텍처는 초기 컴퓨터 시스템에서 주 메모리가 제한적이었던 상황에서 발전했습니다. 이때, 복잡한 명령어 집합은 프로그램 코드를 더 짧게 만들고 메모리를 효율적으로 사용할 수 있게 했습니다. 그러나 이러한 설계는 명령어 길이 변동과 복잡한 디코딩 문

Computer Science

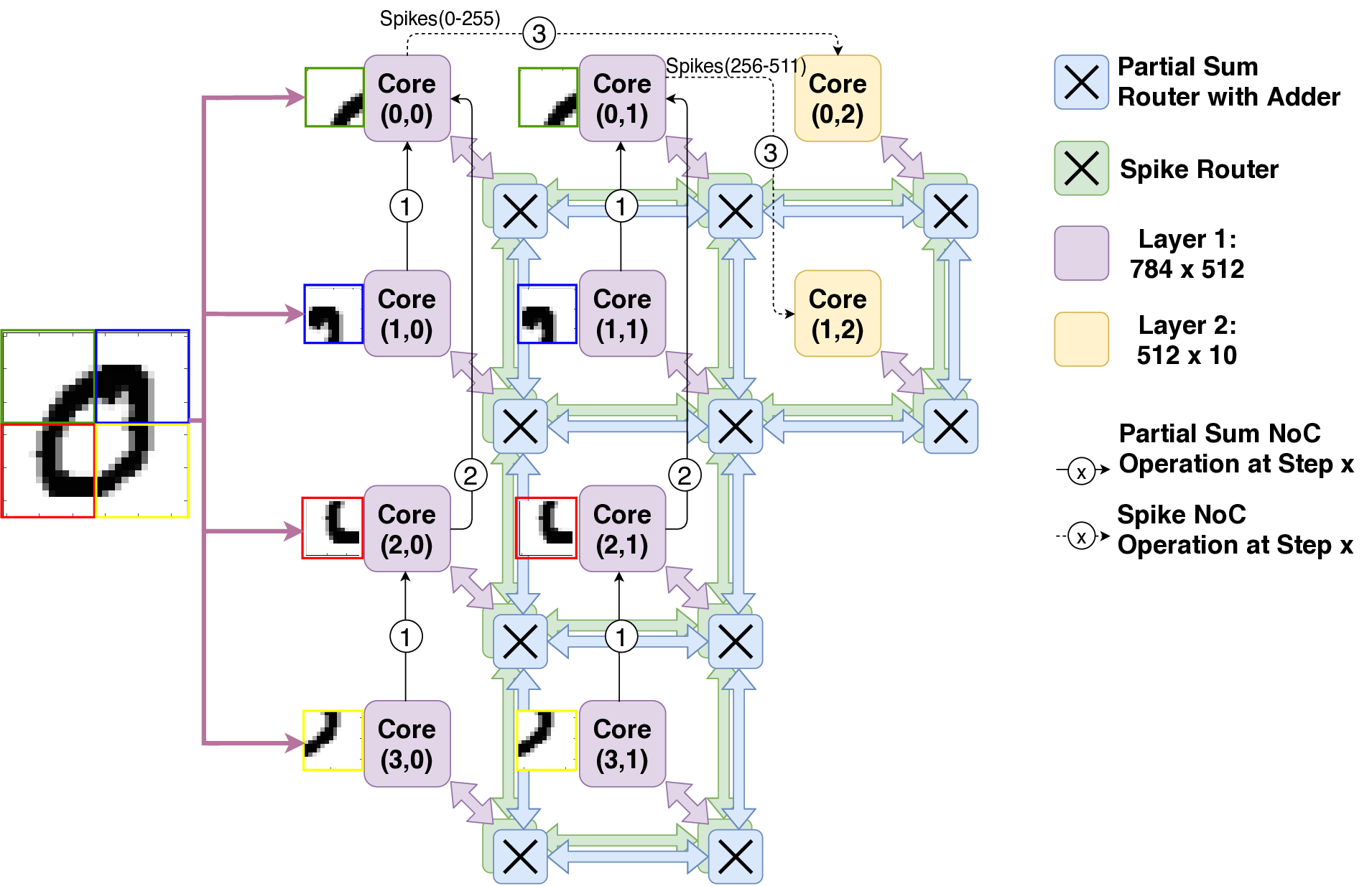

Hardware Architecture