분산 AI 모델 개발을 위한 통합 이벤트 시뮬레이션 프레임워크 UNIFERENCE

UNIFERENCE는 파이토치 디스트리뷰티드와 연동되는 파이썬 기반 이산 이벤트 시뮬레이터로, 통신 원시 연산만을 동기화해 롤백 없이 인과 순서를 보장한다. 실제 하드웨어와 네트워크 파라미터를 프로파일링하거나 가상 슬로우다운 팩터를 적용해 다양한 디바이스와 네트워크 환경을 재현할 수 있다. 실험 결과, HPC 클러스터와 Jetson Orin에서 실행한 LLaMA‑3와 CLIP‑ViT 모델의 실행 시간을 98.6% 정확도로 예측한다. 코드베이스를…

저자: Doğaç Eldenk, Stephen Xia

본 논문은 대규모 인공지능 모델의 추론을 여러 디바이스에 분산시키는 연구가 급증하고 있음에도 불구하고, 이를 체계적으로 평가·재현할 수 있는 표준화된 도구가 부족하다는 문제점을 제기한다. 기존 연구는 전용 테스트베드, 클로즈드 소스 인프라, 혹은 네트워크 시뮬레이터(OMNeT++, ns‑3)와 같은 C++ 기반 툴에 의존해 왔으며, 파이썬 기반 딥러닝 프레임워크와의 연동이 번거롭고, 실제 모델을 실행하지 않는 추정 방식에 머물러 있다. 이러한 한계는 (1) 다양한 하드웨어(고성능 GPU, 저전력 임베디드, 모바일)와 네트워크(5G, 6G, LAN) 환경을 동시에 실험하기 어렵게 만들고, (2) 연구 결과의 재현성을 저해하며, (3) 가상의 미래 하드웨어·네트워크 시나리오를 탐색할 수 없게 만든다.

이에 저자들은 **UNIFERENCE**라는 새로운 이산 이벤트 시뮬레이션(DES) 프레임워크를 제안한다. UNIFERENCE는 파이썬으로 구현되어 파이토치 디스트리뷰티드와 원활히 통합되며, 기존 파이토치 모델 코드를 그대로 사용해 시뮬레이션과 실제 배포를 전환할 수 있다. 핵심 설계는 “통신 원시 연산에만 동기화”한다는 점이다. 각 디바이스는 로컬 클럭을 갖는 논리 프로세스로 동작하고, send/recv/all‑reduce 등 네트워크 이벤트가 발생할 때만 전역 시계와 동기화한다. 이 방식은 낙관적 시뮬레이션에서 흔히 발생하는 롤백을 완전히 배제하고, 인과 순서를 보장하면서도 높은 시뮬레이션 효율성을 제공한다.

UNIFERENCE는 두 가지 실행 모드를 지원한다. 첫 번째는 **Host Emulation** 모드로, 하나의 물리적 호스트에서 여러 논리 디바이스를 스레드(경량 프로세스) 형태로 실행한다. 두 번째는 **Deployment** 모드로, 시뮬레이션 코드를 그대로 실제 하드웨어에 배포해 성능을 측정한다. 두 모드 간 API 차이가 없으므로, 알고리즘의 정확성 검증 후 바로 실환경에 적용할 수 있다.

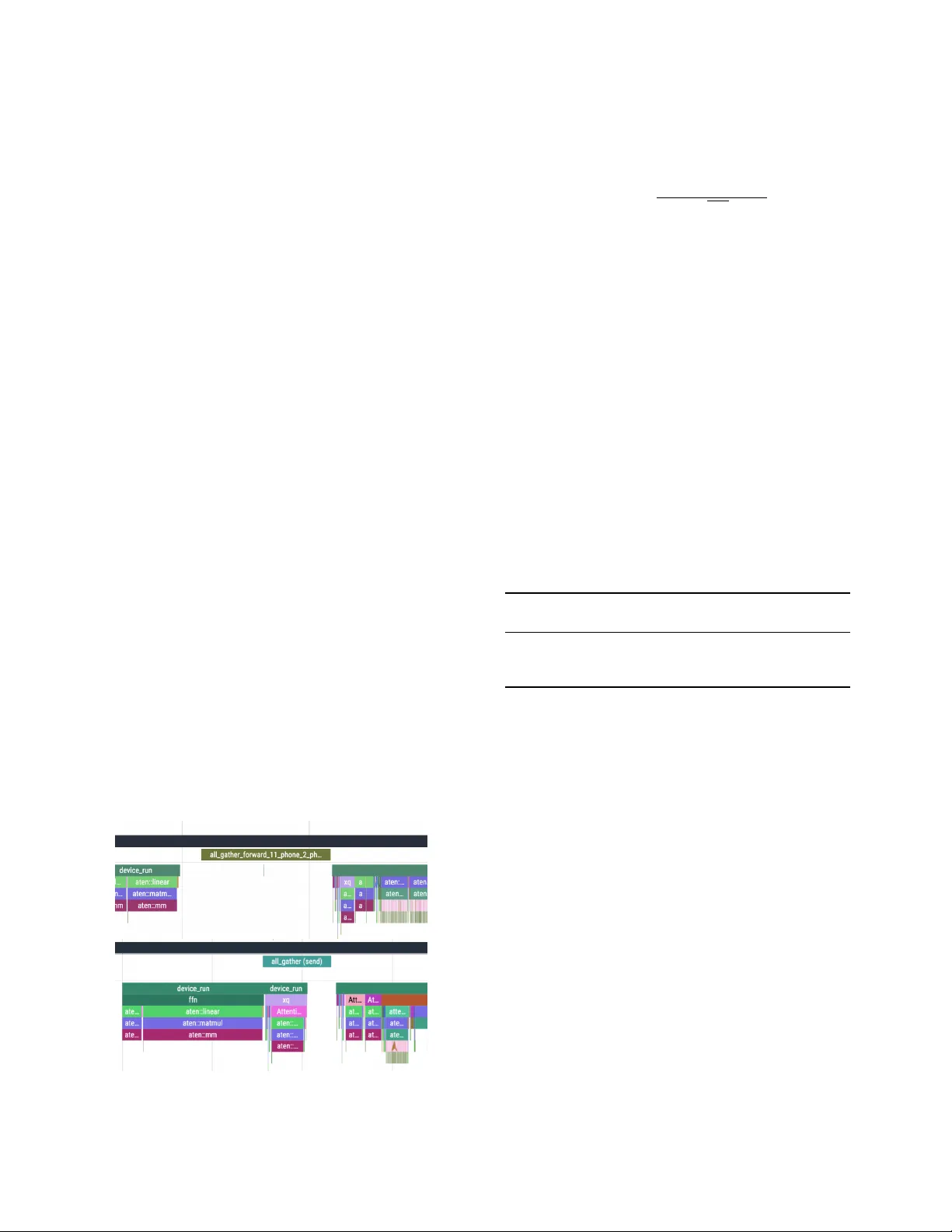

네트워크 모델링은 링 기반 all‑gather와 all‑reduce를 포함한 기본 통신 패턴을 상세히 구현한다. 각 연산은 노드 수(N)와 메시지 크기(M)에 따라 동적으로 대역폭을 할당하고, 사용자는 실제 네트워크 프로파일링 결과를 입력하거나 가상의 지연·대역폭 값을 지정할 수 있다. 또한, **슬로우다운 팩터**를 커널별·코드 구역별로 정의해 접근이 어려운 이종 하드웨어의 성능을 추정한다. 예를 들어, 최신 A100 GPU와 저전력 Jetson Orin을 동일 시뮬레이션에 포함시키고, 각각의 연산에 서로 다른 슬로우다운 값을 적용해 실제 실행 시간 차이를 재현한다.

논문은 UNIFERENCE의 정확성을 검증하기 위해 두 가지 실험을 수행한다. 첫 번째는 **시뮬레이션 오버헤드** 분석이다. 라틴 하이퍼큐브 샘플링을 이용해 자동 회귀 텍스트 생성(LLaMA‑3) 작업의 프롬프트 길이와 스레드 전환 확률(yield)을 다양하게 변형하고, 1·2·4 디바이스 환경에서 실행했다. OLS 회귀 결과, yield 수와 디바이스 수는 통계적으로 유의했지만, 전체 실행 시간에 대한 기여도는 0.001 이하로 실질적 영향을 미치지 않음이 확인되었다. 즉, 스레드 전환에 따른 시뮬레이션 오버헤드가 무시할 수 있을 정도로 낮다.

두 번째는 **시뮬레이션 정확도** 평가이다. 실제 하드웨어(HPC 클러스터의 80 GB A100, Jetson Orin Nano)에서 LLaMA‑3(1 B·3 B)와 CLIP‑ViT 모델을 실행하고, 동일 설정을 UNIFERENCE에 입력해 시뮬레이션을 수행했다. 결과는 R²가 0.97~1.00, MAPE가 0.01%~0.36% 수준으로, 특히 Gloo 백엔드에서는 0.009%의 오차만을 보였다. 네트워크 지연·대역폭을 포함한 복합적인 환경에서도 98.6% 이상의 정확도를 달성했다.

또한, UNIFERENCE를 활용한 **Kilovolts** 최적화 사례를 제시한다. 기존 Voltage 파이프라인 병렬화 기법에 통신‑연산 겹침(overlap) 전략을 적용했으며, 시뮬레이션 기반 프로파일링을 통해 겹칠 수 있는 구간을 자동 탐색했다. 실제 배포 결과, 최대 16%의 추론 속도 향상이 관찰되었다. 이는 시뮬레이션이 설계 단계에서 병목을 사전에 식별하고, 실험 비용을 크게 절감할 수 있음을 보여준다.

종합적으로, UNIFERENCE는 다음과 같은 기여를 한다. (1) 파이썬 친화적인 API와 파이토치 디스트리뷰티드와의 무결점 연동을 제공한다. (2) 통신 원시 연산에만 동기화함으로써 롤백 없이 인과 순서를 보장하고, 시뮬레이션 효율성을 높인다. (3) 실제 디바이스·네트워크와 높은 일치성을 보이며, 다양한 하드웨어·네트워크 시나리오를 가상화한다. (4) 동일 코드베이스로 시뮬레이션·배포를 전환할 수 있어 재현성과 연구 생산성을 크게 향상시킨다.

UNIFERENCE는 오픈소스로 공개되어(https://github.com/Dogacel/Uniference) 연구 커뮤니티가 자유롭게 활용·확장할 수 있다. 향후 작업으로는 자동화된 파라미터 탐색, 더 복잡한 토폴로지 지원, 그리고 대규모 클라우드·엣지 혼합 환경에 대한 시뮬레이션 확장이 제시된다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기