마이크로컨트롤러용 딥러닝 설계, PrototypeNAS로 10분 안에 완성

PrototypeNAS는 제로샷 신경망 구조 탐색을 이용해 MCU에 맞는 DNN을 빠르게 설계한다. 4개의 zero‑shot 프록시를 다목적 최적화에 활용하고, 구조·크기·프루닝·양자화까지 포함하는 통합 검색 공간을 정의한다. 다목적 파레토 집합에서 하이퍼볼륨 서브셋 선택을 통해 3~5개의 대표 모델을 추출한 뒤, 짧은 시간 안에 학습·프루닝·양자화를 수행한다. 12개 데이터셋(이미지, 시계열, 객체 탐지)에서 MCU 제한을 만족하면서 기존 M…

저자: Mark Deutel, Simon Geis, Axel Plinge

본 논문은 마이크로컨트롤러 유닛(MCU)과 같이 메모리·연산량이 극히 제한된 임베디드 환경에서 딥러닝 모델을 빠르고 효율적으로 설계·배포하기 위한 새로운 프레임워크 ‘PrototypeNAS’를 제안한다. 기존의 NAS는 수백·수천 개의 후보 모델을 실제 학습시켜 성능을 평가해야 하므로 시간·자원 소모가 크고, 하드웨어 제약을 충분히 반영하지 못한다. 이를 해결하고자 저자들은 세 가지 핵심 아이디어를 결합한 ‘제로샷 NAS + 멀티오브젝트 최적화 + 하이퍼볼륨 서브셋 선택’ 파이프라인을 설계하였다.

1. **검색 공간 설계**

- 사전 정의된 베이스 아키텍처(예: MobileNetV2, EfficientNet 등)를 ‘슈퍼블록’ 단위로 분해하고, 네 개의 그룹으로 나눈 뒤 각 그룹에 대해 깊이(group depth), 첫 레이어의 커널·스트라이드, 프루닝 비율, 폭 멀티플라이어를 독립적으로 조정한다.

- 전체 검색 공간은 14개의 연속·이산 하이퍼파라미터로 구성되며, 아키텍처 선택, 구조 변형, 크기(프루닝·양자화) 최적화를 하나의 연산으로 통합한다.

2. **제로샷 프록시 앙상블**

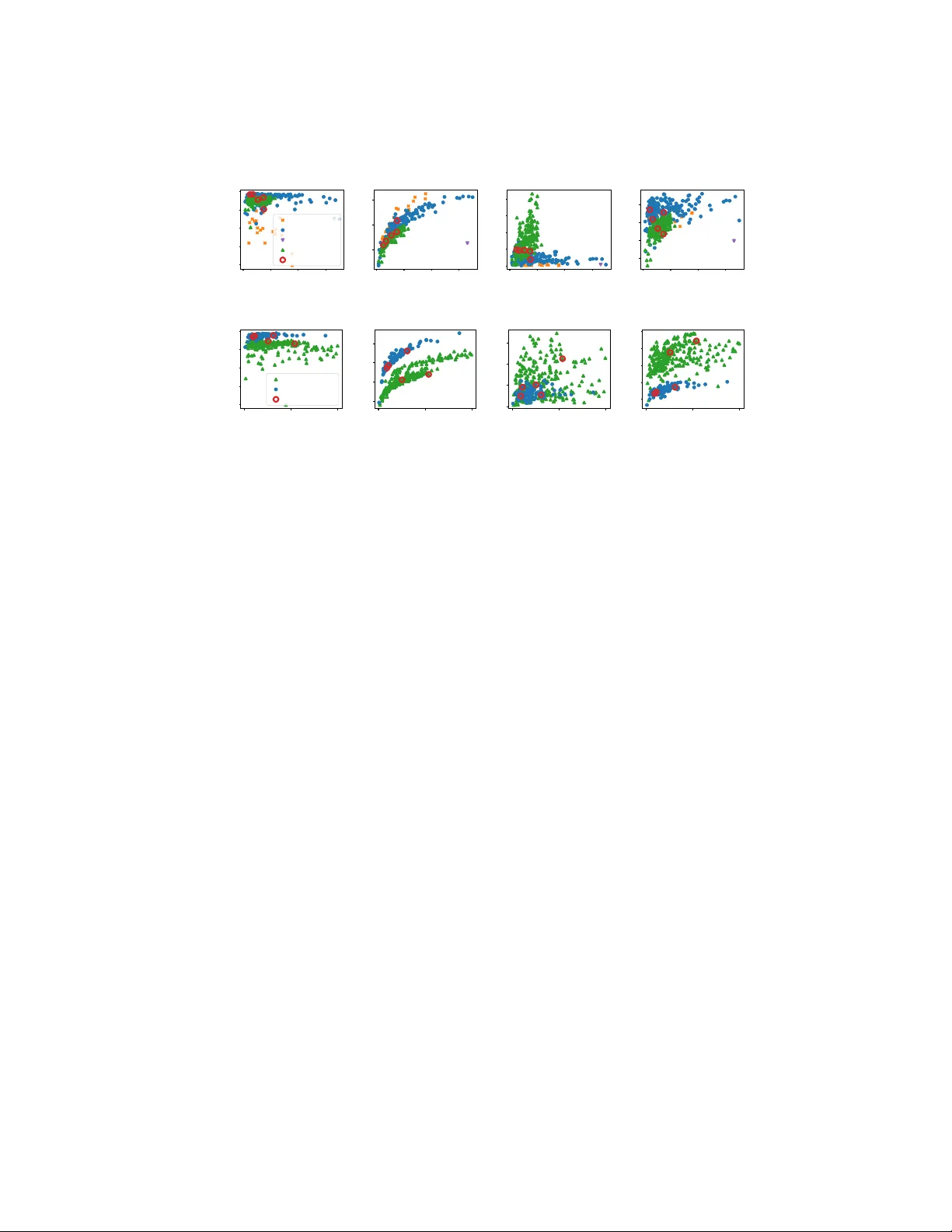

- MeCo, ZiCo, NASWOT, SNIP 네 가지 서로 다른 zero‑shot 프록시를 각각 목적 함수로 사용한다. 이는 각 프록시가 포착하는 네트워크의 선형성, 활성화 분포, 경사 흐름 등 다양한 특성을 동시에 고려하게 한다.

- FLOPs를 비용 목표로 추가함으로써, 정확도와 연산량을 동시에 최소화하는 다목적 최적화를 수행한다.

3. **제약 기반 MOO**

- 최적화는 MCU의 RAM, ROM, FLOPs 한계를 제약조건으로 두고, 목표는 FLOPs 최소화와 프록시 점수 최대화(음수 부호를 사용해 최소화 형태로 변환)이다.

- 탐색은 Bayesian Optimization 혹은 Evolutionary Algorithm 등으로 수행되며, 각 후보는 프루닝·양자화 적용 후 C 코드 변환을 통해 실제 메모리 사용량을 측정한다.

4. **하이퍼볼륨 서브셋 선택**

- 탐색 결과로 얻어진 파레토 최적 집합은 수백 개에 달할 수 있다. 이를 모두 학습·압축하는 것은 비현실적이므로, 하이퍼볼륨 지표를 이용해 k(보통 3~5)개의 대표 모델을 선택한다.

- 진화적 알고리즘을 사용해 초기 인구 2000, 변이율 0.3, 10 000세대 동안 최적화를 진행하고, 하이퍼볼륨 기여도가 높은 솔루션을 유지한다.

5. **데이터셋 평가**

- 12개 데이터셋(이미지 분류: CIFAR‑10/100, GTSRB, Flowers, Birds, Cars, Pets, ArxPhotos; 시계열 분류: Dalia, MAFULDA, BitBrain Sleep; 객체 탐지: COCO 서브셋)에서 실험을 수행하였다.

- 각 작업마다 500번의 탐색 후 파레토 집합을 만든 뒤, 하이퍼볼륨 서브셋을 적용해 최종 5개 모델을 선택, 동일 학습 파라미터(배치 48, SGD lr 0.001, 100 epoch)로 학습하였다.

- 이미지·객체 탐지는 사후 정적 양자화(PTQ)를, 시계열은 양자화 인식 학습(QAT, 추가 15 epoch)으로 최적화하였다.

6. **결과 및 비교**

- PrototypeNAS가 찾아낸 모델은 모두 MCU의 메모리·플래시 제한을 만족하면서, 기존 하드웨어‑인식 NAS인 TinyNAS(MCUNet)와 NATS‑Bench 대비 평균 5 % 높은 정확도를 기록했다.

- 특히 FLOPs와 메모리 사용량을 정확히 예측하는 zero‑shot 프록시 앙상블이 실제 학습 정확도와 높은 상관관계를 보였으며, 프루닝·양자화 조합을 통해 모델 크기를 10배 이상 압축할 수 있었다.

- 탐색 시간은 전체 파이프라인이 수 분 내에 완료돼, “몇 분 안에 MCU 배포 가능한 모델을 얻는다”는 슬로건을 실현했다.

7. **한계 및 향후 연구**

- 현재는 FLOPs와 메모리만을 비용으로 고려하고 있어 실제 레이턴시·전력 소비를 직접 최적화하지 않는다.

- zero‑shot 프록시의 도메인 의존성이 존재하며, 프루닝·양자화 스케줄을 학습 단계와 연계하지 않아 최종 정확도 변동을 완전히 예측하지 못한다.

- 향후에는 하드웨어 측정 기반 레이턴시 모델을 프록시에 포함하고, 프루닝·양자화 스케줄을 학습과 동시에 최적화하는 방안을 모색한다.

결론적으로 PrototypeNAS는 검색 공간의 통합 설계, 프록시 앙상블 기반 다목적 최적화, 하이퍼볼륨 서브셋 선택이라는 세 가지 혁신을 통해 MCU와 같은 극한 환경에서도 빠르고 정확한 DNN 설계를 가능하게 한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기