변동성을 고려한 이진 메모리스트 신경망

본 논문은 이진 가중치를 사용하는 BNN을 메모리스트(ReRAM) 교차배열에 매핑한 BMCNN 구조를 제안하고, R_ON·R_OFF 변동이 정확도에 미치는 영향을 분석한다. 변동 완화를 위해 교차배열 전류 증폭 파라미터 K를 베이지안 최적화로 튜닝하는 방법을 제시하며, MNIST 실험을 통해 90 % 이상 정확도를 유지함을 보였다.

저자: Corey Lammie, Olga Krestinskaya, Alex James

본 논문은 이진 가중치를 활용한 Binarized Neural Networks(BNN)를 메모리스트(ReRAM) 교차배열에 직접 매핑하는 새로운 Binarized Memristive Convolutional Neural Network(BMCNN) 아키텍처를 제안한다. 기존 BNN은 연산량을 크게 줄여 에너지와 면적 효율성을 높였지만, 메모리스트 소자의 비이상성(aging, endurance, variability) 때문에 실제 하드웨어 구현 시 정확도 저하가 우려된다. 이를 해결하기 위해 저자들은 다음과 같은 일련의 설계·시뮬레이션 과정을 수행하였다.

1. **이진 가중치 정규화 및 학습 흐름**

- 가중치를 +1·‑1 로 제한하는 Binary Weight Regularization을 적용하고, 역전파 단계에서 큰 가중치를 t_clip으로 클리핑한다.

- 학습은 오프라인으로 진행되며, 부동소수점(FR‑32) 혹은 8‑bit 고정소수점(FP‑8) 형태로 파라미터를 업데이트한다.

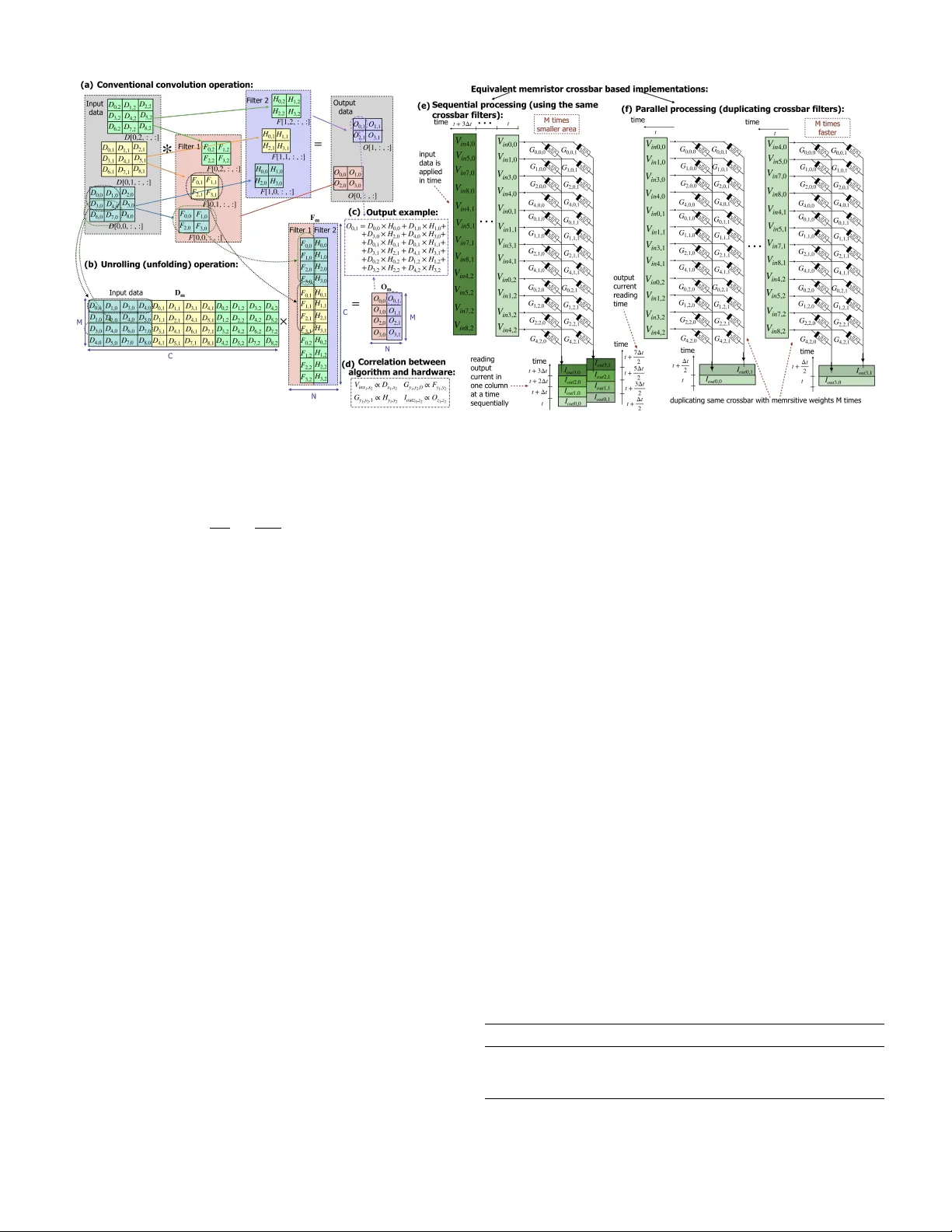

2. **컨볼루션 연산의 행렬 곱 전개**

- 컨볼루션 레이어를 행렬 곱(F_m·D_m) 형태로 변환해 교차배열에 입력한다. 입력 행렬 D_m은 전압 V_in으로, 가중치 행렬 F_m은 이진 저항값(G_i,j)으로 구현된다.

- 전류 증폭 파라미터 K와 기준 저항 G_c를 도입해 양·음 이진 가중치를 구분하고, 출력 전류 I_out을 직접 측정한다.

3. **하드웨어 구조 및 구현**

- 단일 열 교차배열 구조를 사용해 각 레이어마다 별도의 교차배열을 배치한다.

- 교차배열은 순차 처리와 병렬 처리 두 가지 모드가 가능하며, 병렬 모드는 면적을 M배 증가시키는 대신 속도를 크게 향상시킨다.

4. **변동 모델링 및 성능 평가**

- R_ON=1 kΩ, R_OFF=2 kΩ인 TiO₂ 기반 모델을 사용하고, 각 저항값을 가우시안 분포(σ)로 변동시킨다. R_OFF 변동은 R_ON보다 두 배 크게 설정한다.

- σ가 40 이하일 때는 모든 네트워크가 90 % 이상 정확도를 유지하지만, σ가 100을 초과하면 정확도가 급격히 떨어진다. 특히 R_ON·R_OFF 간 상관관계가 존재하면 성능 저하가 더욱 심각해진다.

5. **변동 완화 튜닝 기법**

- 각 레이어별 전류 증폭 파라미터 K를 3000~5000 범위에서 베이지안 최적화(15회 시도)로 조정한다. 이를 TFP‑8 MBNN이라 명명한다.

- 튜닝 후 σ≥100 상황에서도 정확도가 93 % 이상 회복되며, 고정 K를 사용한 FP‑8 MBNN에 비해 평균 2~3 % 향상된다.

6. **실험 설정 및 결과**

- MNIST 데이터셋을 사용해 4가지 옵티마이저(AdaGrad, Adam, SGD m=0, SGD m=0.8)와 배치 크기(64~128), 학습률(1e‑3~1e‑2), t_clip(0.5~1.0) 범위 내에서 베이지안 하이퍼파라미터 탐색을 수행했다.

- 디지털 BNN 구현과 비교했을 때, FP‑8 MBNN은 93.5 %~94.5 % 정확도를 보였으며, TFP‑8 MBNN은 변동이 큰 경우에도 93 %~94 % 수준을 유지한다.

- 전체적으로 변동을 고려한 설계와 튜닝이 메모리스트 기반 BNN의 실용성을 크게 향상시킨다.

7. **결론 및 향후 과제**

- 변동을 고려한 BMCNN은 메모리스트 교차배열의 비이상성을 보상하면서도 높은 정확도를 달성한다는 점을 입증하였다.

- 향후 연구는 전체 회로 수준 구현, 다양한 메모리스트 소재(예: HfO₂) 적용, 그리고 더 복잡한 데이터셋(예: CIFAR‑10, ImageNet)으로 확장하는 것이 제안된다.

본 논문은 메모리스트 기반 이진 신경망이 하드웨어 변동성을 효과적으로 관리할 수 있는 설계·튜닝 프레임워크를 제공함으로써, 저전력·고속 인퍼런스 가속기에 대한 실질적인 로드맵을 제시한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기