지우기 숨김과 구동력 향상을 동시에 구현한 NAND SPIN 기반 자기 비휘발성 플립플롭

CMOS 기술의 미세화로 인한 누설 전력 문제를 해결하기 위해 전원 게이팅 기술과 결합된 비휘발성 플립플롭(NVFF)이 주목받고 있다. 본 연구는 새로운 메모리 소자인 NAND-SPIN을 활용한 혁신적인 자기 NVFF을 제안한다. NAND-SPIN은 지우기(erase)와 프로그래밍(programming)을 위해 각각 스핀 궤도 토크(SOT)와 스핀 전달 토크(STT)를 발생시키는 두 개의 단방향 전류를 순차적으로 인가하여 데이터를 기록한다. 이…

저자: Ziyi Wang, Zhaohao Wang, Yansong Xu

본 논문은 CMOS 기술의 지속적인 미세화로 인해 심각해지는 누설 전력 문제를 해결하기 위한 방안으로, 전원 게이팅(Power Gating, PG) 기술과 결합된 비휘발성 플립플롭(Non-Volatile Flip-Flop, NVFF)에 주목한다. PG는 대기 모드에서 회로의 전원을 차단해 누설 전력을 제거하지만, 기존 휘발성 플립플롭은 데이터를 유지하지 못해 메인 메모리 등에 백업하는 추가 오버헤드가 발생한다. NVFF는 플립플롭에 비휘발성 메모리(NVM)를 통합해 이 문제를 해결한다. 특히 높은 속도, 낮은 전력, 무한한 내구성, 우수한 CMOS 호환성을 가진 자기 터널 접합(Magnetic Tunnel Junction, MTJ)을 활용한 자기 NVFF가 각광받고 있다.

기존의 STT(Spin Transfer Torque)나 SOT(Spin Orbit Torque) 기반 MTJ NVFF는 여러 한계점을 안고 있었다. STT-NVFF는 두 쓰기 방향 간 비대칭적인 스위칭 효율과 소스 저하 효과로 인해 성능이 저하되었다. SOT-NVFF도 양방향 전류가 필요해 소스 저하 효과가 해결되지 않았으며, 상보적 데이터 저장을 위해 두 SOT-MTJ를 반대 방향으로 배치해야 하는 제조 공정의 어려움이 있었다. 또한 대부분의 설계가 백업 동작을 위해 슬레이브 래치에 의존함에 따라 래치 트랜지스터의 크기를 키워야 했고, 이는 CMOS 기반 휘발성 플립플롭 부분의 성능을 저하시키는 요인이 되었다.

이러한 문제들을 극복하기 위해 본 논문은 새로운 메모리 소자 구조인 NAND-SPIN을 기반으로 한 NVFF를 제안한다. NAND-SPIN 장치는 하나의 중금속 스트립 위에 형성된 두 개의 MTJ로 구성된다. 데이터 기록은 두 단계로 이루어진다: 첫째, 중금속에 전류를 흘려 SOT를 발생시켜 두 MTJ를 모두 AP 상태로 초기화하는 '지우기(Erase)' 단계. 둘째, 한 MTJ에 STT 전류를 흘려 AP 상태에서 P 상태로 전환하는 '프로그래밍(Programming)' 단계. 이 방식의 핵심은 두 단계 모두 '단방향' 전류만 필요하다는 점이다.

이러한 NAND-SPIN의 특성을 활용하여 논문은 '지우기 숨김(erase-hidden)' 및 '구동력 향상(drivability-improved)' NVFF를 설계한다. 구체적인 동작은 다음과 같이 네 가지 모드로 구분된다.

1. 활성 모드(Active Mode): 일반 휘발성 플립플롭으로 동작한다. 이 모드 진입 직후 짧은 시간 동안 NAND-SPIN의 두 MTJ를 모두 AP 상태로 지우는 동작이 수행된다. 이 동작은 CMOS 회로와 분리되어 있어 정상 동작에 영향을 주지 않으며, 이후 백업 시에는 프로그래밍만 수행하면 되므로 백업 지연 시간이 단축된다.

2. 백업 모드(Backup Mode): 시스템이 대기 모드로 들어가기 전, 휘발성 래치의 데이터(QT/QC)를 NAND-SPIN에 저장한다. 지우기 단계가 이미 완료된 상태이므로, 데이터 값에 따라 두 MTJ 중 하나만 STT를 이용해 P 상태로 프로그래밍하면 된다. 이때 필요한 단방향 전류는 전원 또는 접지에 직접 연결된 전용 트랜지스터(P2, N2)에 의해 공급되어, 슬레이브 래치의 구동 능력 제약에서 벗어날 수 있다.

3. 대기 모드(Standby Mode): 전원이 차단되어 누설 전력이 제거된다. 데이터는 NAND-SPIN에 비휘발적으로 저장된다.

4. 복원 모드(Restore Mode): 전원이 다시 공급되면, NAND-SPIN에 저장된 상보적 저항 상태(AP/P)를 읽어 휘발성 래치 노드(QT/QC)의 전압 차이로 변환하여 데이터를 복원한다.

제안된 회로의 장점은 다음과 같다. 첫째, 단방향 쓰기 전류를 사용함으로써 소스 저하 효과를 제거했고, 이로 인해 트랜지스터 크기 최적화가 용이해져 구동력이 향상되었다. 둘째, 백업 동작이 슬레이브 래치에 의존하지 않아 설계 유연성이 높아졌다. 셋째, 두 MTJ가 하나의 중금속을 공유하므로 기존 상보적 SOT-MTJ 설계보다 제조 공정이 간소화되고 집적도가 높아진다.

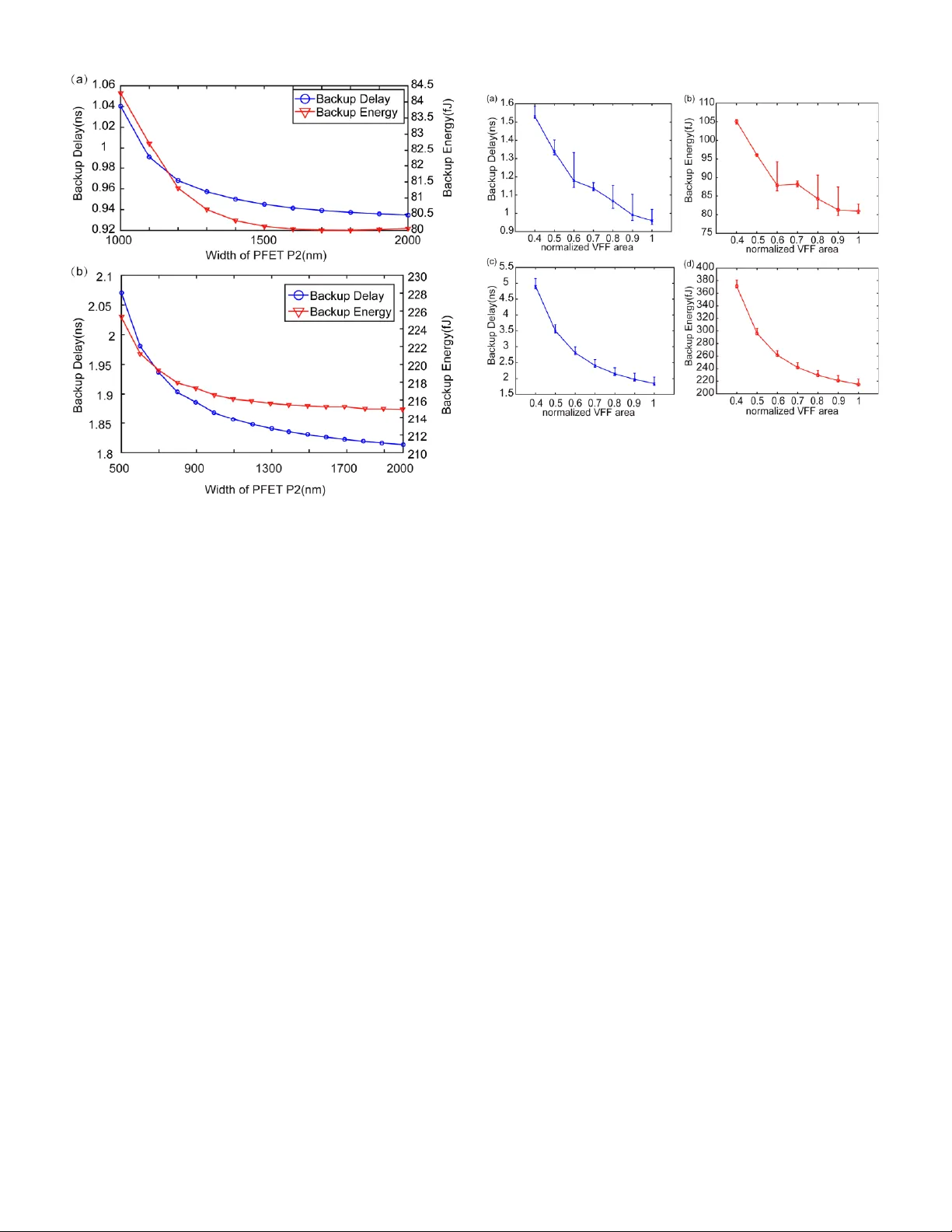

저자들은 40nm CMOS 공정과 SOT-MTJ 모델을 이용한 시뮬레이션을 통해 제안된 NVFF(수직 및 면내 자이오트로피 MTJ 버전)의 성능을 평가했다. 기존의 대표적인 슬레이브 래치 구동형 SOT-NVFF 설계와 비교했을 때, 백업 지연 시간(1.04ns/1.87ns 대 4.95ns/4.32ns), 백업 에너지(84.3fJ/216.5fJ 대 281.7fJ/239.5fJ)에서 현저한 개선을 보였다. 복원 지연 시간과 에너지도 유사하거나 우수한 수준을 유지했다. 이 결과는 NAND-SPIN의 단방향 쓰기 특성과 지우기 숨김 설계가 백업 성능 향상에 효과적임을 입증한다. 결론적으로, 본 논문이 제안한 NAND-SPIN 기반 NVFF는 향상된 성능, 낮은 전력 소모, 높은 설계 자유도 및 제조 용이성을 통해 미래 저전력 고성능 시스템온칩(SoC) 설계에 유망한 솔루션이 될 수 있음을 보여준다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기