딥러닝 가속기를 위한 초고속 무손실 비트플레인 압축 기술

본 논문은 CNN 연산에서 발생하는 대용량 피처맵을 I/O 병목 없이 압축·복원할 수 있는 하드웨어 친화적 무손실 압축기법인 EBPC(Extended Bit‑Plane Compression)를 제안한다. 제로‑런렝스 인코딩과 비트플레인 차분 압축을 결합해 평균 2.2∼5.1배의 압축률을 달성했으며, 65 nm CMOS 구현에서 8‑bit 워드당 600 MHz 처리량을 유지하면서 압축기·복원기가 각각 2.8 kGE·3.0 kGE의 면적만 차지한다…

저자: Lukas Cavigelli, Georg Rutishauser, Luca Benini

본 논문은 현대 딥러닝 가속기에서 가장 큰 전력 소모 원인인 오프‑칩 메모리 I/O를 감소시키기 위해, 피처맵 전용 무손실 압축기법인 EBPC(Extended Bit‑Plane Compression)를 제안한다. 서론에서는 CNN 기반 애플리케이션이 급증함에 따라 임베디드·모바일 시스템과 데이터센터 모두에서 연산량 대비 메모리 대역폭 요구가 크게 증가하고 있음을 지적한다. 특히 최신 네트워크는 가중치를 1‑2비트로 양자화해도 성능 저하가 적지만, 중간 결과인 피처맵은 16‑bit 정수 혹은 8‑bit 정수 형태로 대량 저장·전송이 필요해 전체 에너지 소비의 20∼50%를 차지한다. 기존 연구는 가중치 압축, 스파시티 기반 압축, 복잡한 사전·사후 처리(Huffman, LZW) 등을 주로 다루었으며, 이들은 하드웨어 구현 비용이 크거나 실시간 스트리밍에 부적합한 경우가 많다.

본 연구의 핵심 기여는 다음과 같다. (1) 최신 DNN(ResNet‑50, YOLOv3, MobileNetV2 등)의 피처맵·가중치 메모리 요구량을 정량화해 피처맵 압축의 필요성을 강조한다. (2) 피처맵이 보이는 두 가지 통계적 특성, 즉 높은 제로 비율과 인접 값 간 높은 상관성을 분석한다. (3) 이러한 특성을 동시에 활용하는 새로운 압축 파이프라인을 설계한다. 구체적으로, 입력 스트림을 제로/논제로 구분하고 제로 구간을 고정 길이 버스트 코드와 런‑렝스 인코딩으로 압축한다. 논제로 구분된 값들은 n개의 워드 블록으로 모아 차분(delta) 연산을 수행하고, 차분값을 비트플레인으로 전개한다. 비트플레인 간 XOR 연산(DBX)을 통해 부호 비트를 최소화하고, 이후 사전 정의된 프리픽스 코드 테이블을 이용해 가변 길이 심볼로 인코딩한다. 이 과정은 기존 BPC에 제로‑RLE를 결합한 형태이며, ‘전부 0’ 비트플레인 다중‑알‑0 심볼을 통해 압축 효율을 크게 높인다.

하드웨어 설계에서는 65 nm CMOS 공정으로 압축기와 복원기를 각각 2.8 kGE와 3.0 kGE 면적으로 구현하였다. 파이프라인 구조는 입력 버퍼 → 제로‑RLE 모듈 → 차분·비트플레인 모듈 → 비트플레인 인코더 순으로 진행되며, 600 MHz 클럭에서 1 사이클당 8‑bit 워드(=1 byte)를 처리한다. 복원기 역시 동일한 파이프라인을 역순으로 수행해 실시간 디코딩이 가능하다. 면적 대비 성능을 비교하면, 동일한 처리량을 제공하는 8‑bit MAC 유닛 7개에 해당하는 면적만 차지한다는 점에서 메모리 I/O 절감 효과가 시스템 전체 전력에 미치는 영향을 크게 감소시킨다.

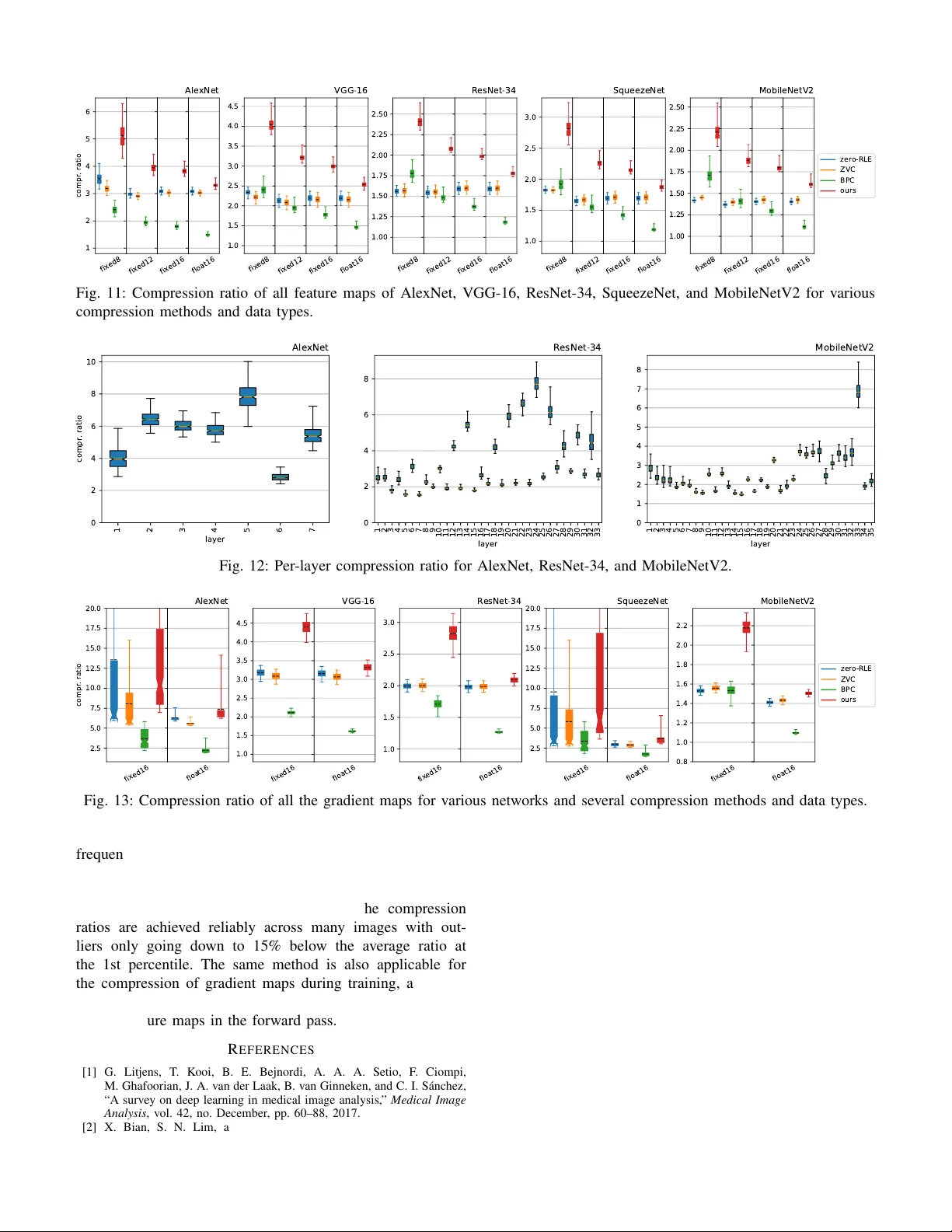

실험에서는 AlexNet, VGG‑16, ResNet‑34, MobileNetV2 네트워크에 대해 8‑bit 양자화된 피처맵을 대상으로 압축률을 측정하였다. 평균 압축 비율은 AlexNet에서 5.1×, VGG‑16에서 4.0×, ResNet‑34에서 2.4×, MobileNetV2에서 2.2×이며, 이는 기존 제로‑RLE, ZVC, CSR 기반 방법보다 45∼70% 높은 수치이다. 또한 훈련 단계에서 발생하는 그래디언트 맵에 동일한 알고리즘을 적용했을 때, 3∼5배의 압축 효과를 얻어 훈련용 메모리 대역폭 병목도 완화한다. 다양한 데이터 타입(8‑bit, 16‑bit 정수, FP16)과 블록 크기에서도 일관된 압축 효율을 보이며, 프레임 간 압축 비율 변동이 낮아 실시간 스트리밍에 적합하다.

논문의 마지막 부분에서는 EBPC의 한계와 향후 연구 방향을 논의한다. 블록 크기가 작을 경우 차분과 XOR 단계에서 얻는 상관성이 감소해 압축 효율이 떨어질 수 있으며, 매우 큰 블록을 사용할 경우 버퍼링 요구가 증가한다. 또한 현재 구현은 65 nm 공정 기반이지만, 최신 7 nm·5 nm 공정에서도 동일한 구조를 적용하면 면적·전력 효율이 더욱 개선될 것으로 기대된다. 향후 연구에서는 동적 블록 크기 조절, 다중 채널 동시 압축, 그리고 메모리 컨트롤러와의 통합을 통해 전체 시스템 수준에서의 에너지 절감 효과를 극대화하고자 한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기