고속 푸리에 변환을 위한 파이프라인 디지털 슬라이싱 무곱셈 버터플라이 온칩 구현

본 논문은 Radix‑2 DIT FFT에서 가장 연산량이 큰 복소수 곱셈을 디지털 슬라이싱 기반의 상수 전용 곱셈기(ROM‑LUT)로 대체하고, 파이프라인 구조를 적용해 FPGA 상에서 549.75 MHz의 최고 클럭을 달성한 설계를 제시한다. 기존 멀티플라이어 기반 버터플라이 대비 약 2.8배 빠른 속도와 적은 게이트 수를 보인다.

저자: Rozita Teymourzadeh, Yazan Samir, Masuri Othman

본 연구는 무선 통신 시스템에서 FFT가 성능 병목으로 작용한다는 점에 착안하여, FFT의 핵심 연산인 복소수 곱셈을 효율적으로 구현하는 새로운 온칩 구조를 제안한다. 먼저 기존의 Radix‑2 Decimation‑In‑Time(DFS) FFT 구조를 간략히 소개하고, 전통적인 버터플라이가 복소수 입력 A·B와 트윌리 팩터 W를 곱하기 위해 4개의 실수 곱셈과 2개의 실수 가산기를 필요로 함을 지적한다. 이러한 복합 연산은 FPGA 내부의 DSP 블록이나 전용 멀티플라이어에 크게 의존하게 되며, 클럭 속도와 면적 효율을 제한한다.

이에 저자들은 ‘디지털 슬라이싱(digit‑slicing)’ 기법을 차용한다. 입력 데이터를 B비트(예: 8비트) 2의 보수 형식으로 표현한 뒤, 이를 b개의 블록(p비트씩)으로 분할한다. 논문에서는 b=2, p=4로 설정하여 4비트 블록 2개로 나누는 방식을 채택하였다. 각 블록은 0~15의 정수값을 가지며, 트윌리 팩터와의 곱셈 결과는 미리 계산된 16가지 경우의 수를 ROM에 저장한다. 이렇게 구성된 ‘단일 상수 곱셈기(Single Constant Multiplier‑Less, SCML)’는 4개의 ROM과 간단한 가산기로 이루어지며, 실제 곱셈 회로를 전혀 사용하지 않는다.

SCML을 파이프라인 형태로 배치하면, 각 슬라이스‑곱셈 단계가 독립적으로 진행되어 연산 지연이 최소화된다. 복소수 덧셈·뺄셈은 고속 가산기인 Kogge‑Stone 및 Stone‑Ling 구조를 적용해 병목을 더욱 줄인다. 전체 버터플라이 구조는 입력 슬라이스 → SCML → 가산기 → 출력 조합 순으로 흐르며, 파이프라인 레지스터가 각 단계 사이에 삽입돼 클럭 주기를 짧게 만든다.

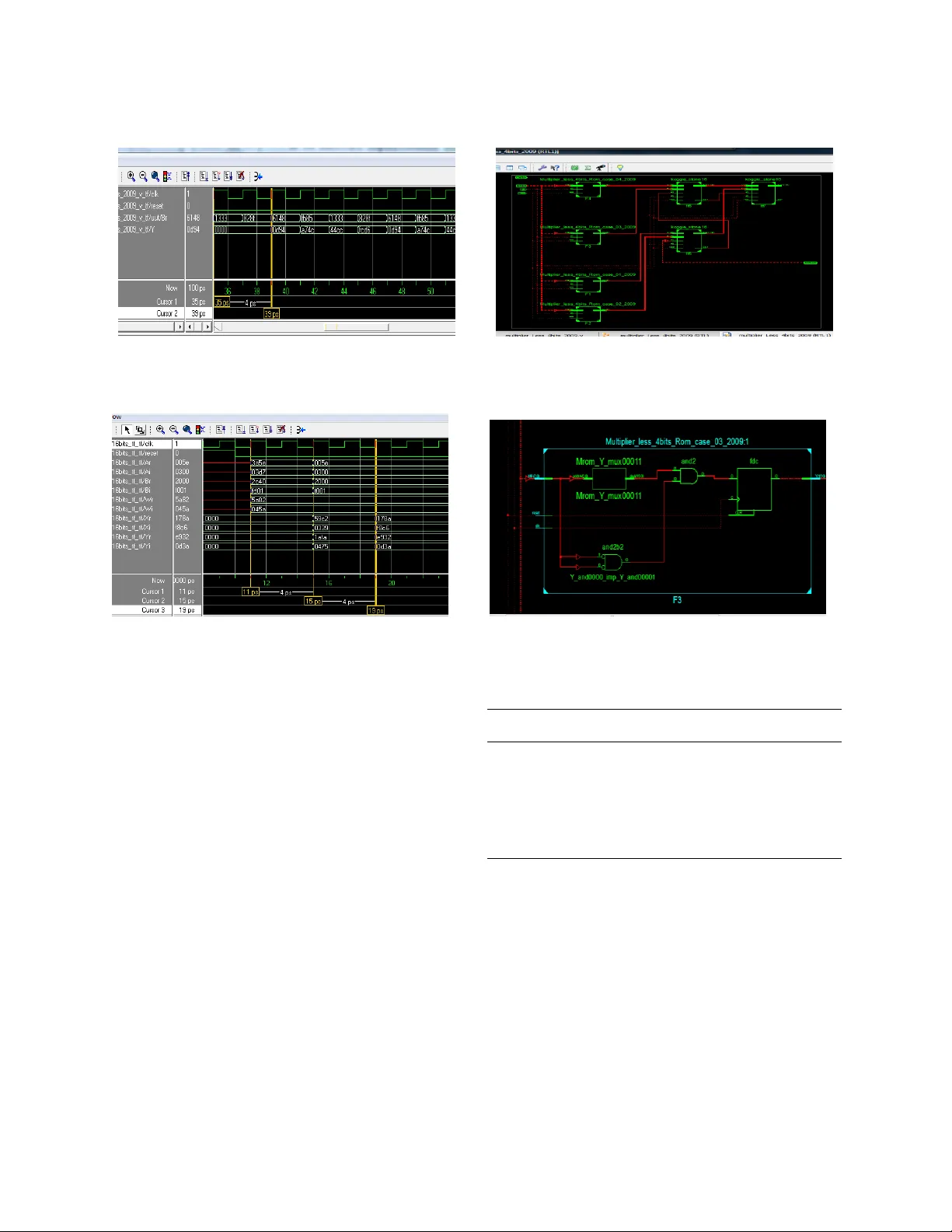

설계는 Verilog HDL로 기술되어 Xilinx ISE 환경에서 합성되었으며, 목표 디바이스는 Virtex‑II XC2V500‑6FG456이다. 합성 결과, 전체 등가 게이트 수는 31 159게이트, 최대 동작 주파수는 549.75 MHz(파이프라인 디지털 슬라이스 무곱셈 버터플라이)와 609.98 MHz(단일 상수 곱셈‑리스 모듈)로 나타났다. 동일한 FFT 구조를 기존 멀티플라이어 기반으로 구현했을 경우, 최대 클럭은 198.987 MHz, 일반 멀티플라이어는 220.160 MHz에 머물렀다. 따라서 제안된 설계는 버터플라이 단계에서 약 276 %·277 %의 속도 향상을 달성했으며, 면적 측면에서도 기존 설계보다 효율적이다.

시뮬레이션 결과는 MATLAB과 ModelSim을 통해 검증되었으며, RTL 스키매틱과 파이프라인 구조가 모두 정상 동작함을 확인했다. 논문은 또한 디지털 슬라이스와 ROM‑LUT 기반 설계가 전력 소모를 감소시킬 가능성을 언급했지만, 실제 전력 측정 데이터는 제공되지 않았다.

결론적으로, 트윌리 팩터가 사전에 알려진 FFT 환경에서 디지털 슬라이스와 상수 전용 LUT를 활용한 멀티플라이어‑리스 버터플라이 설계는 속도, 면적, 설계 복잡도 측면에서 큰 장점을 제공한다. 향후 연구에서는 가변‑정밀도, 다중‑정밀도 FFT, 그리고 다른 고정소수점 포맷에 대한 확장 가능성을 탐색하고, 전력 분석 및 ASIC 구현을 통해 실용성을 더욱 강화할 필요가 있다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기