프로그래머블 CMOS 트랜시버로 구현하는 구조건전성 모니터링

본 논문은 0.5 µm CMOS 공정으로 구현한 고집적 트랜시버 IC를 제시한다. 정수‑N 주파수 합성기와 4‑bit PWM을 이용해 0.1 ~ 2.75 MHz 중심 주파수, 12.7 Vpp의 저왜곡 초음파 파형을 발생시키며, 오프셋‑캔슬링 완전 차동 수신부는 프로그래머블 이득·대역폭, 사분위 믹서를 통해 진폭·위상을 동시에 추출한다. 실험에서는 8개의 PZT 트랜스듀서를 이용한 2‑D 손상 위치 추정을 성공적으로 수행하였다.

저자: Xinyao Tang, Haixiang Zhao, Soumyajit M

본 논문은 구조건전성 모니터링(SHM) 시스템에 필요한 초음파 파형 발생 및 수신 기능을 하나의 CMOS 트랜시버 IC에 통합한 설계와 실험 결과를 상세히 기술한다. 서론에서는 기존의 이산형 SHM 시스템이 무게·부피·전력 소모가 크다는 문제점을 지적하고, 이를 해결하기 위한 고집적 마이크로시스템 접근법을 제안한다. 저자들은 이전에 0.5 µm 2P/3M CMOS 공정으로 구현한 전류 제어형 트랜시버를 개발했으며, 이번 연구에서는 디지털 제어와 프로그래머블 기능을 추가해 성능을 향상시켰다.

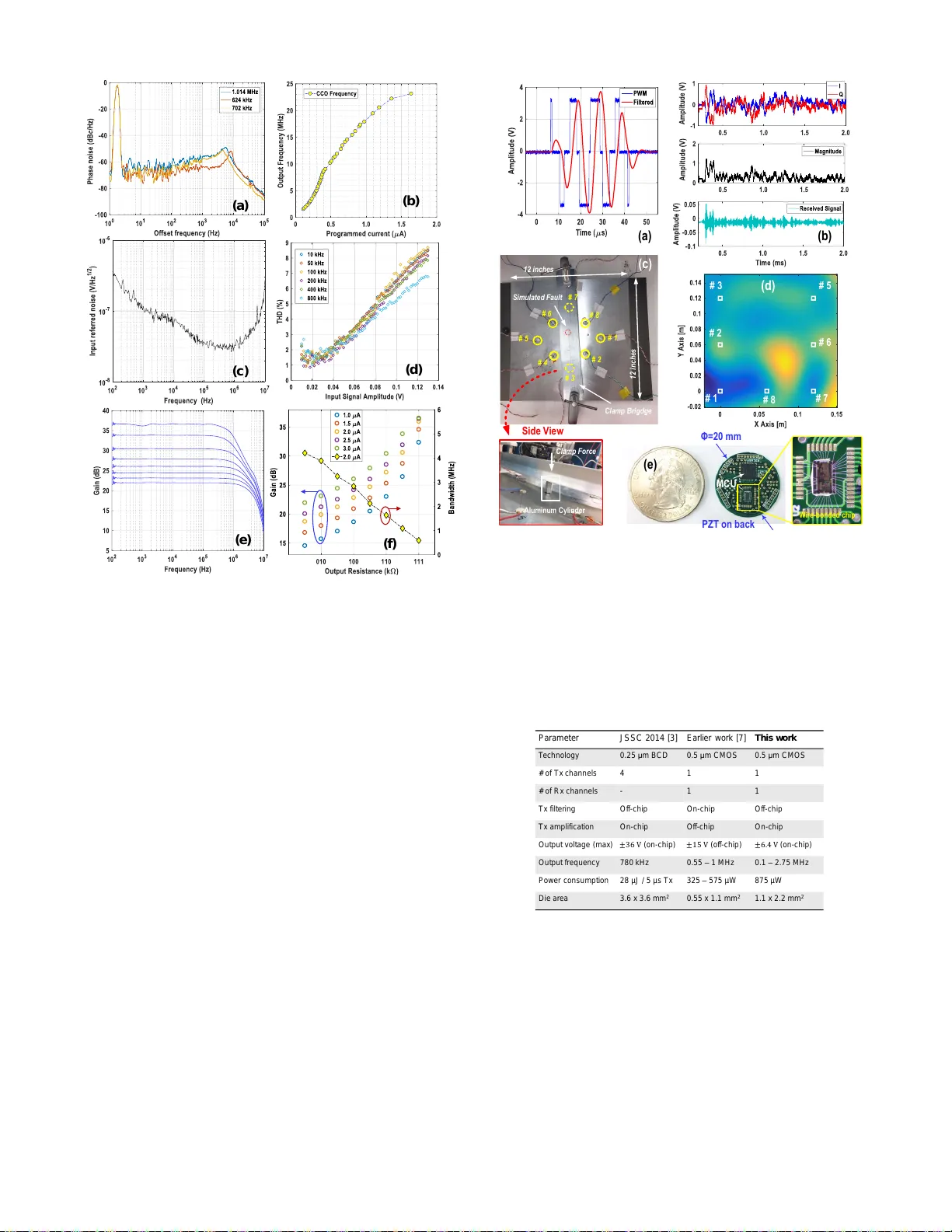

트랜시버 블록 다이어그램(그림 2)에서는 전원(5 V), SPI 인터페이스, 정수‑N 주파수 합성기, 4‑bit PWM, 오프‑칩 LC 저역통과 필터, 전압 증폭 버퍼, 차동 LNA, 패시브 이중 밸런스 사분위 믹서, 2단 저역통과 필터·PGA, 그리고 오프‑칩 ADC가 연결된 구조를 보여준다. 송신부는 32.768 kHz 기준 클럭을 사용해 0.8 ~ 22 MHz 출력 주파수를 생성하는 PLL을 갖는다. PLL은 전류‑스타베드 링 오실레이터와 5‑bit NMOS/PMOS DAC, 넓은 선형 범위 트랜스컨덕터(WLR)로 구성돼 루프 대역폭을 3.5 kHz로 고정하고 위상 마진을 50°로 유지한다. PWM 모듈은 4‑bit 디지털 데이터에 따라 사전 정의된 펄스 폭을 생성하고, 두 개의 XOR 게이트와 180° 딜레이 회로를 이용해 완전 차동 출력을 만든다. 이 PWM 신호는 트랜스듀서 자체 정전용량을 이용한 오프‑칩 LC 필터를 통과해 부드러운 Hamming‑윈도우 사인파 형태로 변환되며, 최대 12.7 Vpp 전압을 제공한다.

수신부는 트리거 펄스 Φt에 의해 동작이 시작된다. 초기 RST 단계에서 모든 회로는 1.3 V 공통 모드 전압으로 리셋된다. 자동 제로화(Auto‑Zero) 회로가 각 저역통과 필터와 PGA에 적용돼 오프셋을 최소화한다. 차동 LNA는 저전류(3 µA) 동작에서 21.6 dB 이득과 4.3 MHz 대역폭을 제공하며, 입력 레퍼런스 잡음 PSD는 21 nV/√Hz이다. 입력 선형 범위는 400 kHz에서 60 mV, 1.2 MHz에서 70 mV (THD < 5 %)로, 실제 SHM에서 관측되는 0.5 ~ 20 mV 신호에 충분히 넓다. 차동 버퍼는 두 단계 CMFB(공통 모드 피드백) 앰프를 사용해 LNA 출력 임피던스를 매칭하고, 사분위 믹서는 패시브 이중 밸런스 구조로 0 dB에 가까운 변환 손실(–4 dB)과 높은 포트 격리를 달성한다. 믹서의 LO 신호는 송신부와 동일한 PLL에서 파생되며, 필요 시 외부 LO 입력도 가능하도록 설계돼 있다.

믹서 출력은 2차 Gm‑C 저역통과 필터를 거쳐 상위 대역의 사이드밴드를 제거하고, 프로그래머블 PGA를 통해 최종 이득을 조정한다. 필터와 PGA는 각각 5‑bit 전류 DAC와 4‑bit 커패시터 DAC로 디지털 제어가 가능해, 다양한 센서와 구조에 맞춰 대역폭과 이득을 최적화할 수 있다.

칩은 1.1 mm × 2.2 mm 면적에 875 µW 평균 전력을 소모한다. 측정 결과는 다음과 같다. (1) PLL 위상 잡음은 10 Hz 오프셋에서 –70 dBc/Hz 수준이며, 주파수 튜닝 곡선은 0.5 ~ 2.75 MHz 범위에서 연속적으로 동작한다. (2) LNA와 버퍼의 입력‑레퍼런스 잡음 PSD와 THD는 시뮬레이션과 일치하고, THD < 5 % 조건에서 최대 입력 전압이 60~70 mV임을 확인했다. (3) 실제 SHM 테스트베드에서는 8개의 PZT 트랜스듀서와 MCU가 탑재된 20 mm 직경의 소형 센서 노드에 본 IC를 연결했다. 전송된 PWM 파형은 Hamming‑형 사인파로 변환되어 트랜스듀서를 구동했고, 수신된 I/Q 데이터는 오프‑칩 ADC를 통해 디지털화된 뒤 딜레이‑앤‑섬 알고리즘에 입력돼 2‑D 손상 위치 지도를 정확히 재구성했다. 손상은 알루미늄 플레이트에 클램프가 가해진 점으로, 손상 지도는 실제 위치와 일치하였다.

마지막으로, 본 설계를 기존의 고전압·다채널 드라이버 IC(예: Guo et al., 2014; Pierco et al., 2015)와 비교한 표(그림 8)에서는 전압·전류·채널 수에서 경쟁력을 유지하면서 전력 효율과 통합도에서 우수함을 보여준다. 결론에서는 온‑칩 ADC와 DSP 통합, 초음파 기반 무선 전력·데이터 전송을 통한 완전 무선 센서 노드 구현을 향후 연구 과제로 제시한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기