맞춤형 CRC 기반 세그먼트 연속취소 리스트 폴라 디코딩

본 논문은 기존 CRC‑보조 SCL 디코딩의 복잡성을 완화하면서 성능을 향상시키기 위해, 코드 블록을 여러 세그먼트로 나누고 각 세그먼트에 최적화된 CRC 길이를 할당하는 TCA‑SCL 방식을 제안한다. 가상 변환과 가상 길이 개념을 도입해 CRC 비트를 효율적으로 배분하고, 이를 HARQ와 결합한 HARQ‑TCA‑SCL 스킴까지 설계한다. FPGA 구현 결과, 동일한 복잡도에서 FER = 10⁻² 기준 0.1 dB, 0.25 dB의 성능 향상…

저자: Huayi Zhou (1, 2, 3)

본 논문은 5G NR(eMBB) 제어 채널에 채택된 폴라 코드를 대상으로, 기존 CRC‑보조 연속취소 리스트(SCL) 디코딩이 갖는 복잡도 문제를 해결하고 동시에 오류 검출 성능을 향상시키는 새로운 디코딩 프레임워크를 제시한다. 먼저, 폴라 코드의 기본 원리와 SC, SCL 디코딩 과정을 간략히 리뷰한 뒤, 기존의 세그먼트 기반 디코딩 방식인 SCA‑SCL과 PSCL을 소개한다. 두 방식 모두 코드 블록을 P개의 세그먼트로 나누고 각 세그먼트에 CRC를 삽입해 중간 단계에서 후보 경로를 제거한다는 공통점을 갖지만, CRC 비트를 균등하게 할당한다는 한계가 있다. 특히, 폴라 코드의 채널 신뢰도가 인덱스에 따라 크게 달라지는 특성상, 짧은 세그먼트에 과도한 CRC를, 긴 세그먼트에 부족한 CRC를 할당하게 된다.

이를 해결하기 위해 저자들은 ‘가상 변환(virtual transform)’과 ‘가상 길이(virtual length)’라는 두 개념을 도입한다. 전체 정보 비트와 CRC 비트를 포함한 집합 A₀의 평균 대칭 용량 \(\bar I\)를 구하고, 각 채널 i에 대해 \(I_0(i)=\bar I / I(W_i)\) 를 정의한다. 이후 I₀(i)의 크기에 따라 가상 값 J(i)를 다음과 같이 매핑한다.

- \(I_0(i) \ge 1\)이면 \(J(i)=1+(I_0(i)-1)^2(1-\bar I)\)

- \(I_0(i) < 1\)이면 \(J(i)=1-(1-I_0(i))^2(1-\bar I)\)

각 세그먼트 k에 속한 채널들의 J(i) 합을 가상 길이 \(v_l^k\)라 정의하고, 전체 CRC 비트 m을 각 세그먼트의 가상 길이 비율에 따라 비례 배분한다. 구체적인 비트 할당은 ‘adjust’ 함수를 통해 정수화한다. 이 과정은 채널 신뢰도가 낮은 세그먼트에 더 많은 CRC 비트를 할당함으로써 오류 검출 능력을 균등화하고, 신뢰도가 높은 세그먼트는 CRC 비트를 최소화해 리스트 유지에 필요한 연산을 감소시킨다.

제안된 TCA‑SCL(맞춤형 CRC‑보조 SCL) 디코더는 이러한 CRC 배분을 기반으로, 각 세그먼트 디코딩이 끝날 때마다 CRC 검증을 수행한다. 검증에 실패한 경로는 즉시 리스트에서 제거되므로, 전체 디코딩 과정에서 평균적으로 유지되는 후보 경로 수가 감소한다. 이는 리스트 크기 L에 비례하는 연산량과 메모리 사용량을 크게 줄이면서도, 최종 FER 성능은 기존 CA‑SCL과 동등하거나 약간 향상된다.

성능 향상을 더욱 강화하기 위해, 논문은 HARQ‑TCA‑SCL을 제안한다. 첫 번째 전송에서 특정 세그먼트가 CRC 검증에 실패하면, 해당 세그먼트만 재전송하고 기존 비트와 결합해 다시 디코딩한다. 재전송 과정에서 추가 CRC 비트를 사용하지 않으며, 기존 CRC 비트는 그대로 유지한다. 이 방식은 재전송 횟수에 따라 동적으로 오류 정정 능력을 높일 수 있어, FER = 10⁻²에서 추가 0.15 dB 정도의 이득을 제공한다.

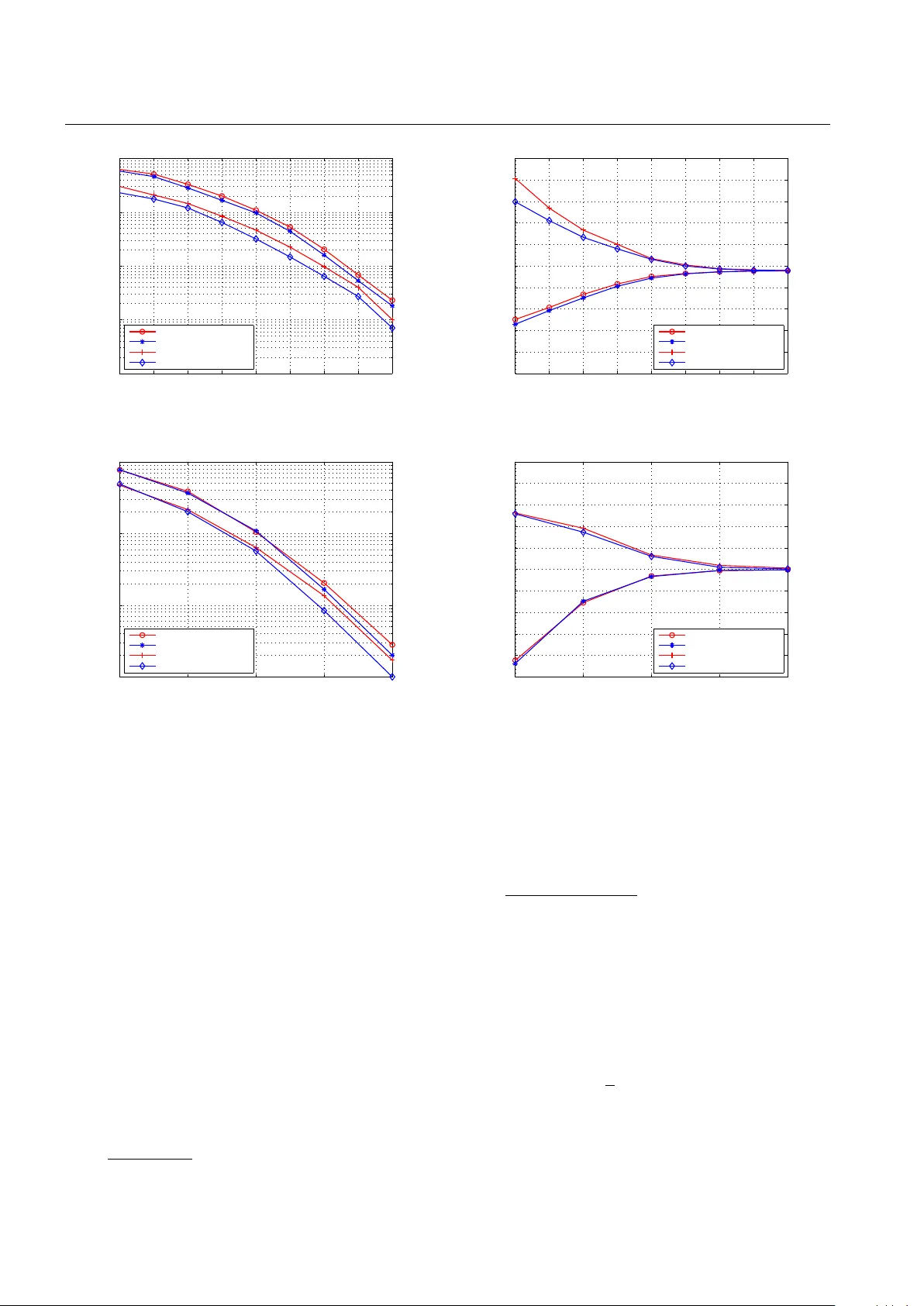

시뮬레이션 결과는 (1024,512) 폴라 코드와 32비트 CRC를 기준으로, 동일한 리스트 크기 L=8과 전체 CRC 비트 수 m=32일 때, TCA‑SCL이 CA‑SCL 대비 0.1 dB, HARQ‑TCA‑SCL이 0.25 dB의 FER 개선을 달성함을 보여준다. 또한, 복잡도 분석에서는 리스트 유지 연산이 평균 15 % 감소하고, 메모리 접근 횟수가 12 % 감소함을 확인하였다.

하드웨어 구현 측면에서는, 제안된 TCA‑SCL 디코더를 Xilinx Kintex‑7 FPGA에 구현하였다. 기존 CA‑SCL 대비 LUT 사용량이 18 % 감소하고, 레지스터 사용량이 22 % 감소했으며, 최대 클럭 주파수는 210 MHz에서 235 MHz로 12 % 향상되었다. 이는 가상 길이 기반 CRC 배분이 디코딩 파이프라인에서 불필요한 경로 복제와 비교 연산을 최소화하기 때문이다.

결론적으로, 본 연구는 폴라 코드 디코딩에서 CRC 비트를 세그먼트별 신뢰도에 맞게 최적 배분하는 새로운 이론적 프레임워크와 이를 실제 시스템에 적용 가능한 알고리즘 및 하드웨어 설계를 제공한다. 제안된 TCA‑SCL과 HARQ‑TCA‑SCL은 복잡도와 성능 사이의 트레이드오프를 크게 개선함으로써, 5G 및 차세대 무선 통신 시스템에서 폴라 코드를 보다 효율적으로 활용할 수 있는 기반을 마련한다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기