직접 변환 펄스 UWB 트랜시버 설계와 구현

본 논문은 FCC 규격(3.1~10.6 GHz, –41.3 dBm/MHz) 하에서 고속 데이터 전송과 짧은 거리 통신을 목표로 하는 초광대역(UWB) 시스템의 핵심 설계 과제를 제시한다. 1비트·4비트 ADC 선택, 디지털 백엔드 병렬화, RAKE·Viterbi 수신기, 직접 변환 RF 프론트엔드 등을 포함한 1세대와 2세대 트랜시버 구조를 비교·분석하고, 동일 사양의 이산형 프로토타입을 통해 알고리즘 검증 및 성능 평가를 수행하였다.

저자: Raul Blazquez, Fred Lee, David Wentzloff

본 논문은 초광대역(UWB) 통신이 직면한 시스템‑레벨 과제들을 체계적으로 분석하고, 이를 해결하기 위한 두 가지 트랜시버 설계와 이산형 프로토타입 구현을 제시한다. 먼저, FCC가 허용한 3.1~10.6 GHz 대역에서 –41.3 dBm/MHz 이하의 전력 스펙트럼 밀도를 만족해야 하는 제약을 강조한다. 이러한 제약은 RF 프론트엔드가 500 MHz 이상 넓은 대역폭을 커버하면서도 낮은 NF와 충분한 선형성을 유지해야 함을 의미한다. 또한, 다중 경로에 의한 RMS 딜레이 스프레드가 20 ns 수준으로 심각하고, 협대역 간섭이 존재할 수 있기 때문에, 수신기는 채널 임펄스 응답 추정, RAKE 결합, Viterbi 디코딩 등 복합적인 디지털 신호 처리가 필요하다.

첫 번째 세대 트랜시버는 0.18 µm CMOS 공정으로 구현된 시스템‑온‑칩(SOC) 형태이며, 4 × 플래시 인터리브 ADC를 이용해 2 GS/s 샘플링을 수행한다. 이 설계는 다운컨버터를 배제하고 직접 베이스밴드 펄스를 디지털화함으로써 회로 복잡성을 크게 낮췄다. 디지털 백엔드에서는 타이밍 동기화와 패킷 동기화를 전적으로 수행하며, 병렬화 기법을 통해 프리앰블 동기화 시간을 70 µs 이하로 단축한다. 실험 결과, 193 kbps 전송을 성공적으로 시연했으며, 전력 소모의 절반 이상이 디지털 연산과 ADC에 집중된다는 점을 확인했다.

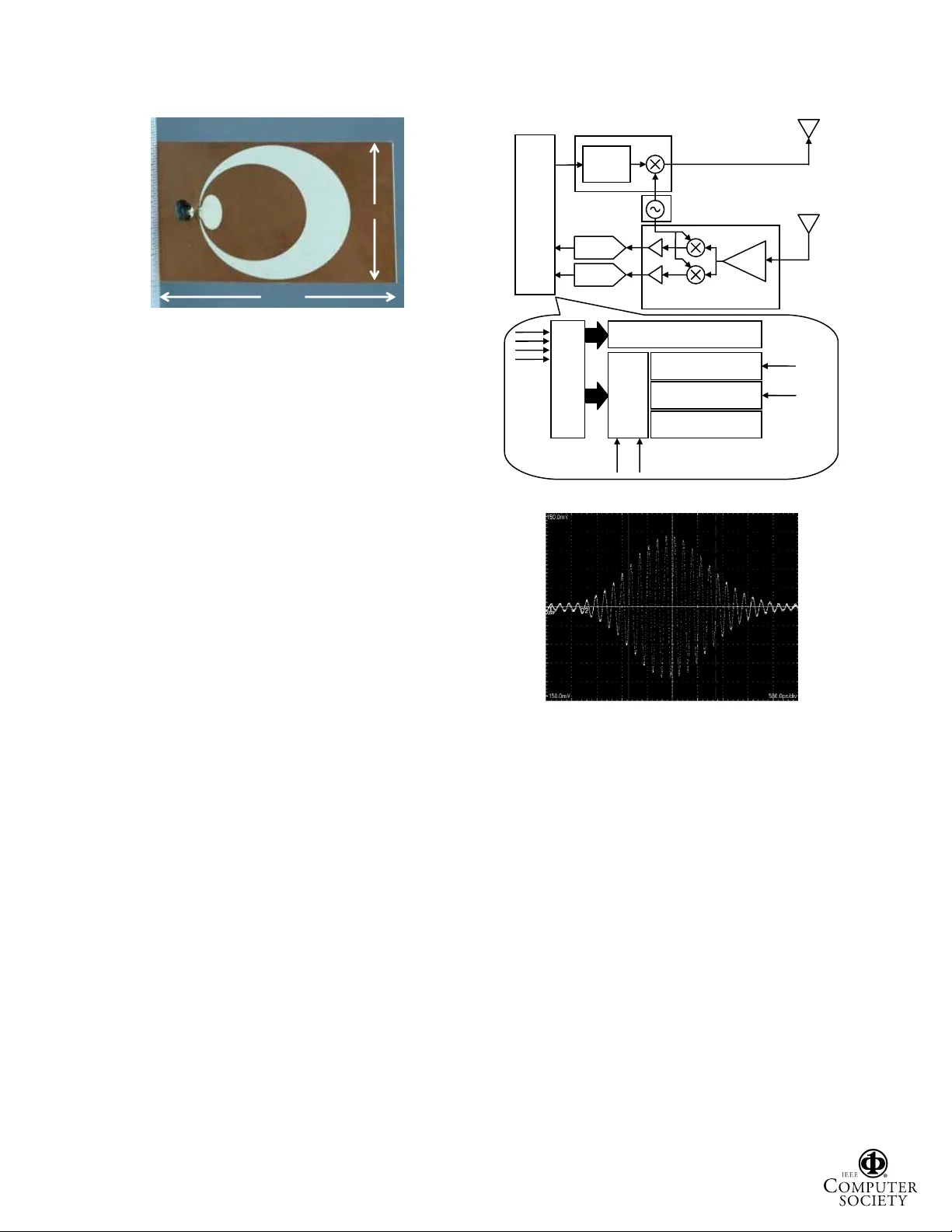

두 번째 세대는 3.1~10.6 GHz 전체 대역을 커버하도록 설계된 직접 변환(Direct‑Conversion) 구조이다. 14개의 서브밴드 중 하나를 선택해 500 MHz 대역폭 펄스를 업컨버트하고, I/Q 두 채널을 각각 5‑bit SAR ADC로 디지털화한다. 프리앰블 동안 4‑bit 정밀도로 채널 임펄스 응답을 추정하고, 이를 기반으로 프로그래머블 RAKE와 Viterbi 디코더를 구동한다. 디지털 백엔드는 협대역 간섭을 탐지하고 주파수를 추정해 프론트엔드에 노치 필터를 적용함으로써 간섭 억제 기능을 제공한다. 이 설계는 전력·연산 복잡도와 서비스 품질 사이의 트레이드오프를 유연하게 조절할 수 있게 한다.

동일 사양의 이산형 프로토타입도 구축하였다. 4.2 cm × 2.7 cm 크기의 평면 안테나는 3.1~10.6 GHz 전역에서 균일한 방사 특성을 보이며, 500 MHz 대역폭 펄스를 5 GHz 캐리어에 변조한 파형을 생성한다. 프로토타입을 이용해 다양한 변조 방식과 채널 모델을 테스트함으로써, 디지털 백엔드의 채널 추정 정확도, RAKE 결합 효율, Viterbi 디코딩 성능을 정량적으로 평가하였다. 결과는 디지털 병렬화와 고속 인터리브 ADC가 프리앰블 동기화 시간을 수십 마이크로초 수준으로 단축시키고, 5‑bit SAR ADC가 잡음 제한 구간에서 충분한 SNR을 제공함을 보여준다.

논문은 설계 트레이드오프를 다음과 같이 정리한다. (1) ADC 해상도는 잡음 제한 구간에서는 최소화해 전력 소모를 줄이고, 간섭 제한 구간에서는 4‑bit 정도로 충분히 성능을 확보한다. (2) 직접 변환 구조는 다운컨버터를 없애 전력 효율을 높이지만, I/Q 불균형과 DC 오프셋을 디지털 보정으로 보완해야 한다. (3) 프로그래머블 RAKE와 Viterbi 디코더를 결합하면 다중 경로와 협대역 간섭을 동시에 억제하면서도 시스템 전력을 절감할 수 있다. (4) 디지털 백엔드와 ADC가 전체 전력의 절반 이상을 차지하므로, 저전력 디지털 설계와 효율적인 병렬 처리 아키텍처가 핵심이다.

결론적으로, 본 연구는 UWB 통신 시스템이 직면한 RF·디지털 복합 과제를 두 단계의 트랜시버 설계와 이산형 프로토타입을 통해 실증함으로써, 고속 데이터 전송, 짧은 프리앰블, 그리고 전력 효율성 사이의 균형을 달성할 수 있음을 입증하였다. 향후 연구는 더욱 높은 데이터 레이트(>100 Mbps)와 저전력 ASIC 구현을 목표로, 고정밀 채널 추정 및 적응형 간섭 억제 알고리즘을 심화시킬 예정이다.

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기